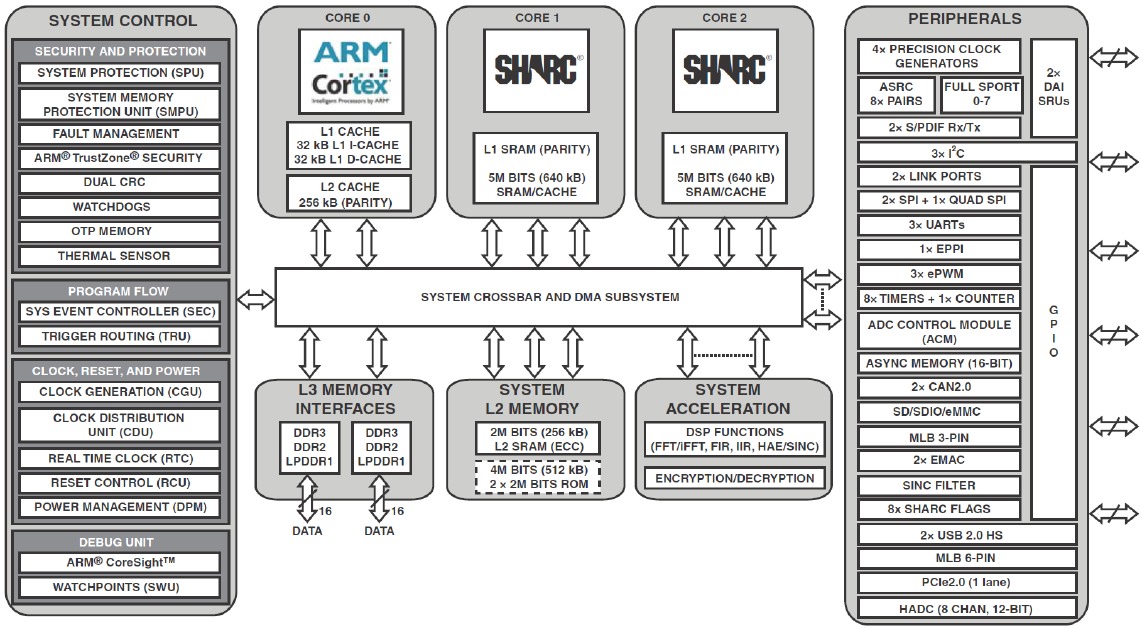

The SHARC DSP family has long been a design staple of mid-range and high-end audio, industrial and other digital signal-processing intensive applications. With its two new series of products, Analog Devices delivers dual-core SHARC to the market for the first time. And the ADSP-SC58x devices also integrate an ARM processor core to tackle system control code functions (Figure 1).

Figure 1. A migration from the 65 nm to 40 nm process node enables a high degree of integration in Analog Devices' new products, along with a performance boost and power consumption reduction.

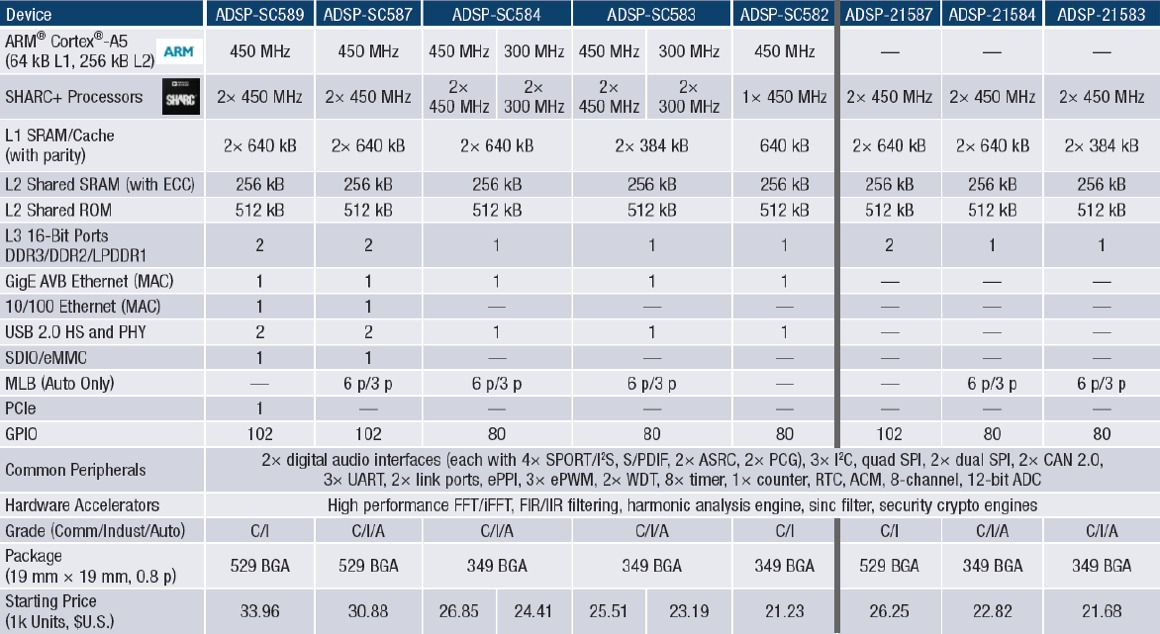

With these new chip families, Analog Devices debuts a new generation of SHARC core, dubbed "SHARC+." Backwards code-compatible with previous SHARC offerings, SHARC+ adds byte addressability and 64-bit double precision floating-point support, and integrates up to 640 KB of L1 cache per core with parity error detection capabilities. The dual SHARC+ cores also share 256 KB of L2 RAM with ECC facilities, along with 512 KB of ROM. While most of the new family members include dual SHARC+ cores, the eight-device family includes one member, the ADSP-SC582, with a single SHARC+ core (Table 1).

Table 1. Pricing for Analog Devices' SoCs, supporting single- and dual-core SHARC+ DSP configurations along with an optional ARM Cortex-A5 core, begins at $17 (quantity 10,000) and $21.23 (quantity 1,000).

In addition to the SHARC+ cores, five of the eight devices also embed a 300 or 450 MHz ARM Cortex-A5 processor core (matching the corresponding SHARC+ core(s) clock speed) complete with 64 KB of L1 cache and 256 KB of L2 RAM. The Cortex-A5, introduced in late 2009, currently anchors the low end of ARM's ARMv7 32-bit core product line; 64-bit ARMv8 products have received most (albeit not all) of ARM's attention in recent times. But Colin Duggan, DSP product line director at Analog Devices, strove to calibrate feature set expectations during a recent briefing.

The Cortex-A5, he offered, was selected for its performance-vs-power efficiency combination, particularly considering the alternative processing capabilities of other on-chip resources. In fact, for at least some of the chips' target applications, he suggested that the Cortex-A5 might deliver more performance than is necessary. Analog Devices' customers, he offered, won't be trying to run a full-blown Android operating system, for example, only networking software stacks and other more focused code.

What are those other on-chip resources? They include a brand new, up to 2048-point complex FFT/iFFT accelerator with up to 18 GFLOPS of claimed total performance. This function block handles single-precision floating-point data, implements vector complex multiplication for windowing and frequency domain filtering, and includes a dedicated, high-speed DMA controller with pipeline mode. Additional DSP-acceleration "engines" include FIR and IIR filters, and SINC filters and harmonic analysis engines (the latter functions commonly used in motor control and other industrial applications). You'll also find an 8-channel stereo asynchronous sample rate converter, primarily intended for audio processing, and a variety of cryptographic and other security-related acceleration blocks.

At the heart of this combination of increased integration and boosted performance versus prior SHARC offerings is a lithography transition from 65 nm to 40 nm, delivering increases in both clock speed and transistor budget. This process evolution has also, according to Duggan and Marketing Manager Andrew Lanfear, significantly reduced the power consumption necessary to achieve a particular level of performance. Combining the two SHARC+ DSPs, together capable of 5.4 GFLOPS (1.8 GMACs), with the up-to-18 GFLOPS FFT/iFFT function block results in approximately 24 GFLOPS of peak real-time digital signal processing at sub-2 W typical power consumption, according to Analog Devices. The result, in many cases, is elimination of any need for costly, bulky and failure-prone heat sinks and fans.

Various devices in the two product series come in commercial, industrial and/or automotive temperature grades. Note, too, the 349- and 529-ball BGA package options; they take up the same amount of board space, but the latter supports a second 16-bit DDR SDRAM interface, along with a higher general-purpose I/O pin count. Both product families are supported by Analog Devices' CrossCore Embedded Studio tool chain, as well as Micrium’s RTOS and Linux (for ARM). And Analog Devices has also assembled the $495 ADSP-SC58x EZ-KIT development suite, combining an evaluation board, ICE-1000 JTAG emulator and one-year licenses to all necessary software.

Both the development kit and preliminary product samples are now available, with more robust "X-grade" samples slated for the first quarter of 2016, followed by a production release one quarter later. These new devices' DSP core enhancements, combined with first-time multi-core integration, should enable them to keep pace with (if not accelerate beyond) competitors' offerings at similar price points, particularly, when considered in the context of their optional ARM core integration.

New SHARC ADSP-SC58x

mowood60 Tue, 06/30/2015 - 07:35Looks like a great new product family, a leadership audio DSP / control processor portfolio.

Congratulations to the team at ADI.

ADI's SHARC/ARM

Willaz Wed, 07/01/2015 - 11:37I’m impressed with ADI’s new SHARC/ARM product offerings. More DSP horsepower at lower power is always a winner and the addition of the ARM Cortex-A5 clearly adds new utility to the product family.

Add new comment