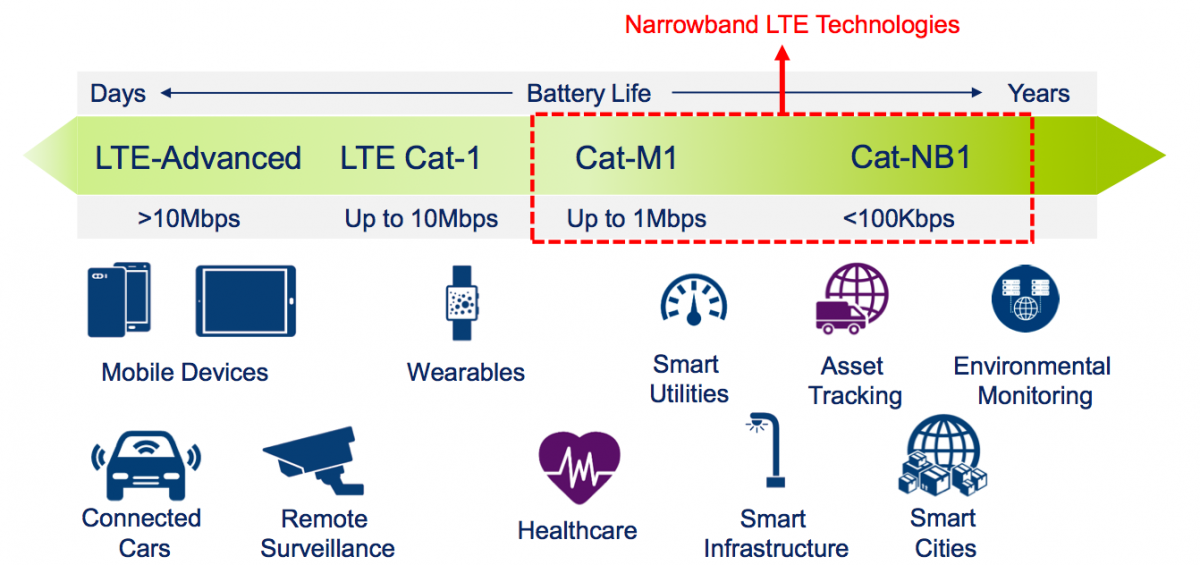

In March, InsideDSP covered the CEVA-X4, the first member of the company's cellular DSP core family based on its CEVA-X architecture framework, and focused on smartphones and tablets that support gigabit-per-second LTE-Advanced and LTE-A Pro protocols. In June, the company introduced the CEVA-X2, with half the scalar units of its bigger sibling (two versus four), and targeting wearables and other devices that harness 10 Mbps LTE-Cat 1 (formerly known as LTE-M Category 1). And now the company has introduced the CEVA-X1, which includes a single scalar unit and is tailored for cellular-connected IoT devices based on the 1 Mbps Cat-M1 (formerly LTE-M Category 0) and 100 Kbps Cat-M0 standards, and also supports global location and navigation systems such as GPS and GLONASS (Figure 1).

Figure 1. The new CEVA-X1 focuses on applications based on narrowband LTE protocols, leaving higher-bandwidth LTE standards to its higher-end family members.

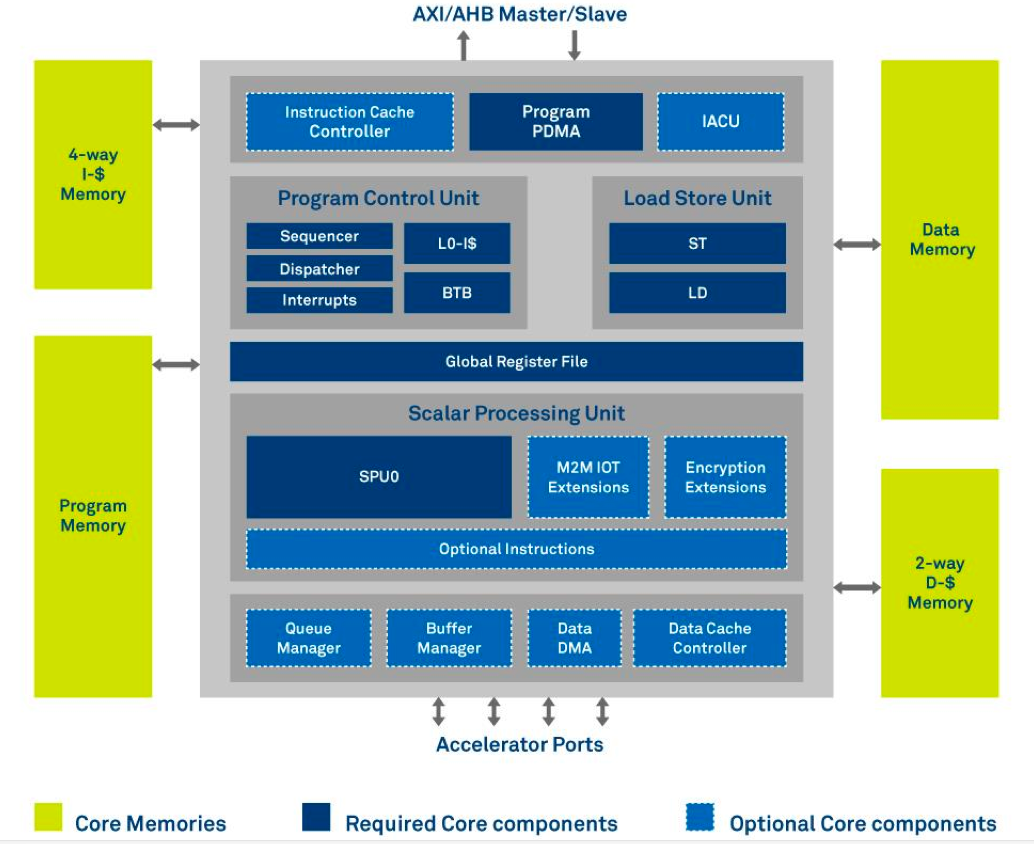

The CEVA-X1's single scalar unit, fed by 64-bit load and store data memory buses, contains two 16x16 MAC units which can alternately be configured as a single 32x32 MAC. In comparison, the CEVA-X2 and CEVA-X4 contain two and four times as much data memory bus width and MAC capabilities, respectively (Table 1). Equally reflective of the CEVA-X1's simplification versus its bigger family siblings, its SIMD architecture and VLIW parallelism are also more limited, at 32-bit and 4-way, versus 128-bit and 7-way on the CEVA-X4, for example. In all other respects, however, features are identical across all three members: a 10-stage pipeline architecture, an optional IEEE-compliant single-precision floating point unit per scalar unit, optional data and instruction caches, and optional support for dynamic branch prediction and CEVA-Connect protocol-based co-processors and other hardware accelerators, such as the company's Cat-M1 Turbo decoder.

|

Feature |

CEVA-X1 |

CEVA-X2 |

CEVA-X4 |

|

Pipeline |

10-stage |

10-stage |

10-stage |

|

VLIW |

4-way |

5-way |

7-way |

|

SIMD |

32 bit |

64 bit |

128 bit |

|

Scalar units |

1 |

2 |

4 |

|

MACs |

Two 16x16 bit or one 32x32 bit |

Four 16x16 bit or two 32x32 bit |

Eight 16x16 bit or four 32x32 bit |

|

Data memory buswidth |

64 bit (load and store) |

128 bit (load and store) |

256 bit (load and store) |

|

Single-precision FPU |

0-1 |

0-2 |

0-4 |

|

Dynamic branch prediction unit |

Optional |

Optional |

Optional |

|

Data cache |

Optional |

Optional |

Optional |

|

Instruction cache |

Optional |

Optional |

Optional |

|

CEVA-Connect support |

Optional |

Optional |

Optional |

Table 1. CEVA-X family features.

And how does the CEVA-X1 compare to the CEVA-XC5 and CEVA-XC8, covered by InsideDSP a year ago and targeting seemingly similar markets? According to Emmanuel Gresset, CEVA's Business Development Director for Wireless and Wireline Communications, while the cores' applications may be similar at first glance, a look at the details exposes their differences. Notably, the CEVA-XC5 and CEVA-XC8 offer varying numbers of scalar and vector execution units; vector support is completely absent from the CEVA-X1 (Figure 2). On the one hand, the CEVA-XC5 and CEVA-XC8's higher performance enables them to support not only cellular data and location services but also, for example, a full software-based Wi-Fi implementation. However, both the CEVA-XC5 and CEVA-XC8's die size and power consumption exceed that of the CEVA-X1 (Gresset declined to provide specifics for either metric). And because they're based on a prior-generation DSP architecture, they require a separate control processor. One of the key advancements the company touts for its new CEVA-X framework is its extended ISA; CEVA claims that this improvement enables it to efficiently support both DSP and control processing functions.

Figure 2. The CEVA-X1 omits the vector processing capabilities present in the CEVA-XC5 and CEVA-XC8; it also offers fewer processing resources compared to the CEVA-X2 and CEVA-X4.

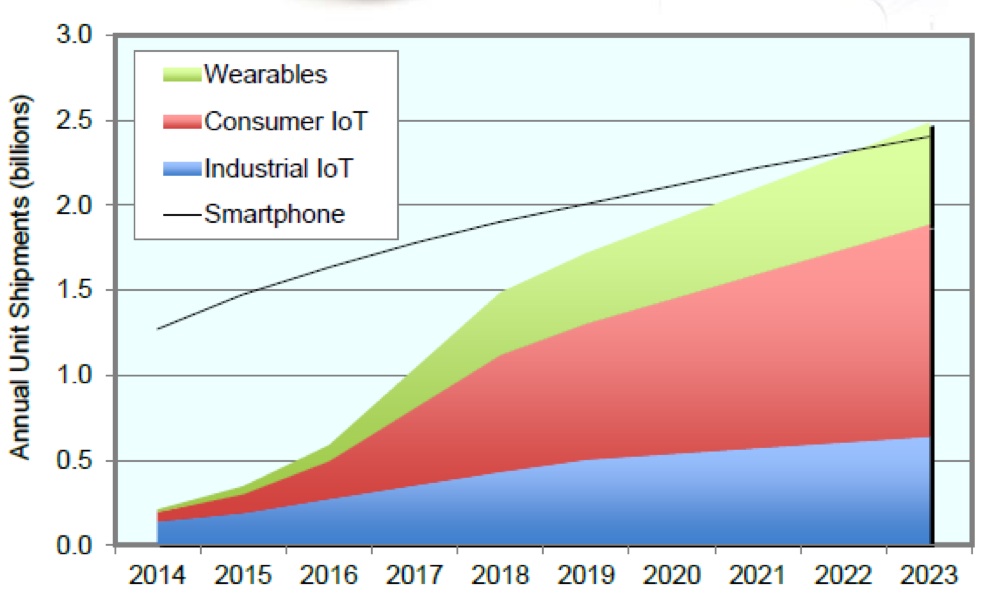

Gresset forecasts that all CEVA-X family members are capable of running at up to 1.5 GHz when fabricated on a 16nm FinFET process. However, given CEVA-X1 applications' low-end/low-cost and "5-10 years of operation on a single AA battery" power consumption targets, he notes that the new core will likely run at much slower speeds in real-life designs, and will be built on more mature 40 to 55 nm process nodes. The CEVA-X1, along with optional Cat-NB1 and other coprocessors, is now available for licensing and implementation. Given the robust market projections for narrowband LTE in IoT and other applications, first shown in InsideDSP's CEVA-XC5 and CEVA-XC8 coverage last year, CEVA's product announcements are timely (Figure 3).

Figure 3. Today's dominant smartphone market will be matched (and eventually exceeded) in aggregate by wearable and IoT devices in the coming years, according to market analysts such as the Linley Group.

Add new comment