DSP processor core licensor CEVA has added to its portfolio with the new CEVA-X1643 and CEVA-XC323 DSP cores. The cores are the next-generation successors to the CEVA-X1641 and CEVA-XC321, respectively. The new cores roughly double the clock frequency of the prior offerings to 1 GHz and are targeted for 40 nm implementation. Both cores rely on a VLIW architecture combined with SIMD capabilities, and the XC323 adds a vector computation unit. The X1643 targets a broad range of applications from handsets and portable media applications to wireless base stations. The XC323 specifically targets 4G LTE wireless base stations.

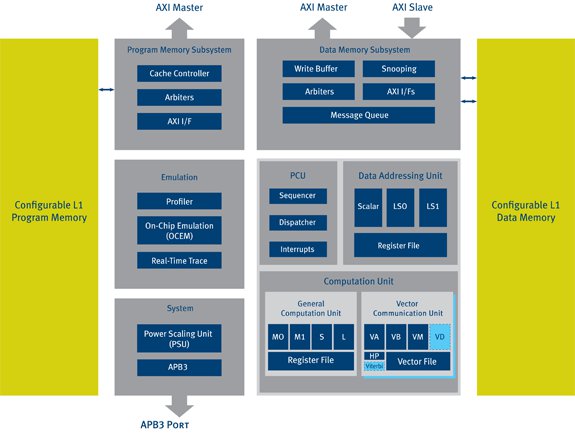

Figure 1 below depicts the XC323 core. The block diagram is virtually identical to that of the X1643 with the exception that the X1643 does not include the vector computation unit shown in the lower right portion of the diagram.

Figure 1. Block diagram for CEVA-XC323 Core

The two new cores are based on a similar microarchitecture. The cores can process as many as eight instructions per cycle and 16 SIMD sub-operations per cycle.

While the architectures of the XC323 and XC1643 are very similar, the two cores target different types of SoC architectures. The X1643, which is aimed at a broad range of applications, is intended for use by hardware-centric design teams that favor using accelerator blocks for functions such as Viterbi decoding. In contrast, the XC323, which is targeted specifically at 4G cellular base stations, is intended for use in software-centric SoCs with minimal reliance on external accelerators. The XC323 core includes a vector computation unit that can accelerate wireless communication tasks such as Viterbi decoding. According to CEVA, the vector computation unit incorporates an instruction set that enables the core to implement almost all of the functions required in a cellular baseband including DFT, high-precision FFT, channel estimation, MIMO detectors, and interleaver/deinterleaver. CEVA states that the XC323 can implement all 4G physical layer processing (including legacy 3G and 2G support) in software with the exception of the requirement for an external turbo decoder block.

Recognizing that Texas Instruments (TI) has long been dominant in high-performance DSP chips, CEVA is supporting its new cores with its own implementations of the DSP intrinsic functions provided by TI for its C6x processors. Intrinsic functions are small assembly-language-optimized DSP-centric functions that can be invoked within a C or C++ program to boost the performance of an application written in C or C++. CEVA is not the first company to duplicate TI’s intrinsic functions, but the support will be welcome to design teams with legacy C6x code.

CEVA focused on energy efficiency in both of the new core designs, attacking both static and dynamic power consumption. The designs utilize partitioned power domains and separate clocks for major functional blocks. The power scaling unit implements multiple operating modes with the ability to remove power and clock from major blocks.

The X1643 is intended to operate up to 1 GHz and is projected to consume 0.18mW/MHz at full speed, according to CEVA. While that dynamic power specification is the same as the prior generation CEVA-X1641, the ability of the new core to halt clocks to unused functional units will yield lower power use in actual applications, according to CEVA. The XC323 is also intended for operation at up to 1GHz; its dynamic power consumption is projected to be 0.36 mW/MHz, according to CEVA.

From a performance perspective the new cores will certainly best earlier CEVA cores simply due to faster clock speeds. The widely used X1641 is designed for operation up to 600 MHz. Thus far CEVA has not provided a meaningful comparison of the performance advantage the 1643 will offer relative to the 1641. According to CEVA, the X1643 requires just 18 MHz to implement an AMR-NB (Adaptive Multi Rate – Narrow Band) vocoder.

CEVA has projected the performance of the XC323 in a 4G LTE wireless base station. For a single cellular sector, the receiver chain will require three cores plus a dedicated turbo decoder, and the transmitter chain would need a single core, according to CEVA.

Performance, of course, must be considered relative to cost, and that ultimately comes down to die size. Both of the new cores were developed for a 40 nm process. Excluding memory, the X1643 core will measure 0.3 mm², and the XC323 will measure 1.7 mm², according to CEVA.

CEVA says that its licensees have been working with the X1643 for several months, and that chips based on the X1643 will likely debut in the first half of 2011. CEVA has delivered an early version of the XC323 core to one licensee and plans to deliver a final release in December. Chips based on the XC323 are likely a year away.

Add new comment