Texas Instruments (TI) is continuing to expand its cellular base-station SoC family, incorporating multiple instances of the TMS320C66x (C66x) DSP core that the company introduced in early 2010. The new TMS320TC16612 (TCI6612) and TMS320TC16614 (TCI6614) chips target femtocell (approximately 64 users) and picocell (approximately 128 users) base station designs. For the first time, TI has also integrated a CPU core―an ARM Cortex-A8―to handle control and management functions. The new chips will support both 3G WCDMA and 4G LTE links.

The TCI6612 integrates two C66x cores. According to TI, this SoC can support either full-rate LTE or the fastest HSPA+ flavor of WCDMA, but not both at the same time. In contrast, the TCI6614 integrates four C66x cores and TI claims that this enables it to simultaneously support full-rate HSPA+ and LTE. The new products share the same overall architecture (referred to as “Keystone” by TI) that underlies the TCI6616 SoC announced last fall, which targets the macrocell 3G and 4G base stations that form the foundation of cellular networks. TI also announced a follow-on, higher-end TCI6618 SoC earlier this year based on the Keystone architecture.

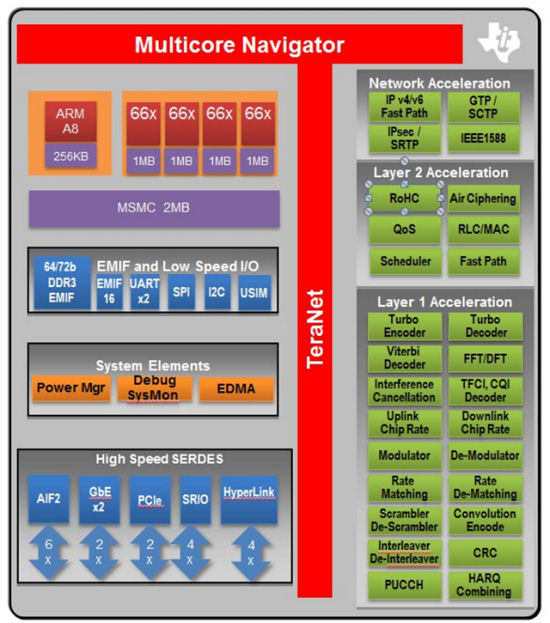

Figure 1 depicts the new TCI6614. The key processing elements are the DSP and CPU processor cores, numerous coprocessors that accelerate network-layer functions, and various accelerators for physical-layer DSP functions such as FFTs and turbo decoding, which are central to cellular standards.

Figure 1. The TI TCI6614 small-cell base-station SoC combine four C66X DSP cores, an ARM Cortex-A8 RISC core, and a host of accelerators for various DSP kernels and algorithms.

“Teranet”, TI’s marketing moniker for the company’s non-blocking switched interconnect fabric, links the processing elements. Previously, TI has said that the fabric supports an aggregate bandwidth of 2 Tbps.

The queue-based Multicore Navigator is the other important element in the SoC architecture. A DSP core that needs to access an accelerator function block places a data packet in a queue and adds a descriptor detailing the required processing function. The Multicore Navigator finds the correct processing resource, dispatches the queued data, and returns the results without requiring any further supervision by the DSP core. According to TI, the Multicore Navigator can even dispatch queued data to an available resource on a different TCI661x chip when a base station design combines multiple SoCs.

According to TI, an integrated CPU is a good for the new chips based on the CPU performance required for femtocells and picocells. Whereas larger cells require multiple DSP chips to handle physical layer processing, and higher performance CPUs for control, TI believes the Cortex-A8 is well matched to the control processing requirements of smaller cells.

It’s worth noting that TI chose to use the Cortex-A8, which has significantly lower floating-point performance compared to the newer Cortex-A9. TI states, however, that the DSPs will handle all floating-point operations, leaving the CPU core to manage control plane tasks. The C66x core was notable, when introduced last year, for supporting floating-point math. In fact, it marked the first instance of a manufacturer adding floating-point support to its highest-performing DSP core. Floating-point support simplifies software development, but historically has come with a price premium and performance penalty that has made it unattractive for high-performance DSP applications. TI believes that this trade-off has shifted, as base stations use more complex algorithms (making floating-point support more useful) and as TI has been able to boost floating-point performance.

In terms of performance, the C66x core remains at or near the top of its class according to BDTI DSP Kernel Benchmarks™ (Full benchmark results are available on BDTI’s web site.) At launch, the C66x core operating at 1.25 GHz earned a fixed-point BDTImark2000 score of 16,690―the highest score in the industry at the time. Freescale subsequently introduced a 1.2 GHz version of its SC3850 core, which achieved a score of 18,500. TI the boosted the C66x clock speed to 1.5 GHz in February and achieved the current top score of 20,030. The 1.2 GHz version of the C66x also earned a top score of 10,720 for floating-point performance in the BDTImark2000 benchmark. The 1.5 GHz version has pushed that score to 12,860. In contrast, the Freescale SC3850 does not support floating-point math.

Regarding clock speeds on the new chips, all that TI will say for now is that its DSP and CPU cores will operate at a maximum of 1.0 or 1.2 GHz. The SoCs are built on a 40 nm process and will sample in the third quarter of 2011. According to TI, the TCI6612 will dissipate 10 watts while the TCI6614 will dissipate 11 watts. TI is utilizing existing higher-performance chips to allow design teams to start now on product developments that will utilize the new SoCs. The company will offer a development platform that combines the TCI6616 SoC with one of its Integra processors based on an ARM core. The company will also supply what it calls “near production ready” software for base stations. The offering stops short of what might be called a complete reference design. TI insists that its customers prefer to modify the software and otherwise differentiate product offerings, and therefore do not need production-ready software.

Prior to the TI announcement, small-cell systems specialist Ubiquisys, based in the UK, announced a collaboration that will yield products based on TI’s SoCs. The Ubiquisys announcement didn’t mention the TCI6612/14 SoCs (which had not been announced at the time of the Ubiquisys announcement). But it’s a safe bet that the new TI chips will find a spot in upcoming Ubiquisys femtocells and/or picocells. The growing breadth of TI’s base-station SoC family could prove to be a strategic advantage for the company, because system manufacturers will be able to use some of the same software across a broad range of products from small cells to macro cells to future cloud RAN (Radio Access Network) cells.

However, the market for small cells is still embryonic. Some observers see the need for much lower cost implementations with reduced feature sets for residential and enterprise deployment. TI, conversely, projects that the small cell market will demand the same fundamental feature set that customers expect in macrocells. For instance, TI expects numerous outdoor installations of picocells by enterprises and therefore believes that those designs will have to support mobile users in automobiles. Exactly how the small-cell market evolves will in no small part determine the success that TI finds with its newest SoCs.

Add new comment