In September, ARM announced its latest high-performance processor core–the long-rumored Cortex-A15, code-named Eagle. The announcement contained few details, but did set out some aggressive performance targets, and also made it clear that ARM’s ambitions extend beyond hand-held devices to cellular base-stations, networking equipment, servers, and other performance-hungry infrastructure applications.

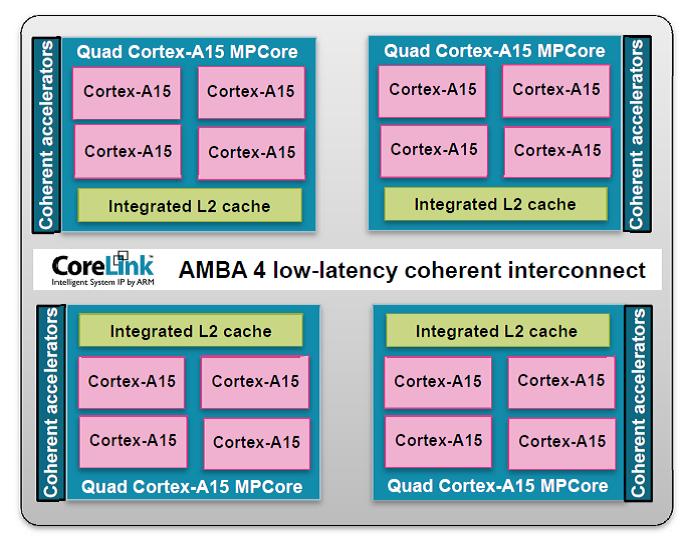

One clue to ARM’s ambitions is the relatively short but significant list of new features contained in the Cortex-A15 compared to its predecessor, the Cortex-A9. Several of these features appear to be driven by requirements of infrastructure applications (rather than mobile handsets, netbooks, or typical embedded applications). For example, the Cortex-A15 will include support for a larger physical address space (up to one terabyte), and more extensive support for error-correction-control memory to enable fault tolerance. In addition, the core will come equipped with an AMBA 4 bus interface enabling coherent interconnection of multiple clusters of Cortex-A15 cores (see figure); a single cluster can contain up to four cores. The new core will also include hardware support for virtualization.

As for performance, ARM projects that a dual-core Cortex-A15 processor designed for mobile applications will achieve five times the performance of today’s single-core Cortex-A8 chips. According to ARM, the higher per-core performance will be enabled by a combination of the Cortex-A15’s new microarchitecture, more advanced manufacturing processes (ARM envisions the Cortex-15 being implemented in 28 nm or 32 nm processes), and physical IP blocks developed by ARM specifically for the Cortex-A15. In chips designed for infrastructure applications (and therefore tuned for performance rather than energy efficiency), ARM envisions 8 or 16 Cortex-A15 cores running at up to 2.5 GHz. While these performance projections are impressive, ARM offered no hint of the cost of attaining this performance: no silicon area or power consumption data was provided.

Another important unknown is the Cortex-A15 microarchitecture. ARM stated that the new core will use a new microarchitecture, but did not provide any specifics. Likely the new microarchitecture will be more complex than its predecessors, in order to enable higher clock speeds and parallelism. This will make it more challenging for compilers to generate efficient code—an increasingly critical consideration as applications grow in complexity and developers have less time to tinker with optimizations.

ARM plans to release the Cortex-A15 to its chip partners around the end of this year. Chips based on the new core are unlikely to appear for at least a year after that.

If the Cortex-A15 delivers on ARM’s performance projections, and does so with reasonable silicon area and power consumption, it will be a strong addition to ARM’s processor line-up. In that case, it will likely gain traction in high-end client devices, infrastructure equipment such as cellular base stations, and demanding embedded applications. We await more detailed disclosures from ARM and its partners regarding the Cortex-A15 microarchitecture, power consumption, and silicon area.

Add new comment