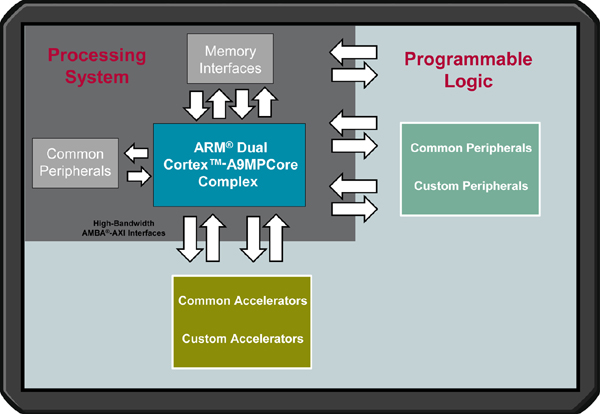

Xilinx recently unveiled a new chip architecture integrating an ARM processor with an FPGA fabric. This platform centers around a dual-core ARM Cortex-A9 processor complex, including hardened memory interfaces and peripherals. The platform architecture, shown in Figure 1, is intended to behave like a CPU first and an FPGA second. Specifically, the CPU will boot independently—without requiring that the FPGA first be configured. Xilinx is targeting markets that require both complex software and high-performance data processing, such as automotive driver assistance, intelligent video surveillance, industrial automation, aerospace and defense, and next-generation wireless products.

Figure 1: Platform Architecture

The architecture will provide significant CPU processing power with a dual-core ARM Cortex-A9 at up to 800 MHz (including the NEON SIMD extensions) in addition to the FPGA fabric. There are approximately 2,500 signal connections between the processing system and the programmable logic. The interconnect uses the recently developed, FPGA-friendly AMBA 4.0 protocol, developed by ARM with input from Xilinx. These interfaces are intended to increase the bandwidth and decrease the latency available for CPU-coprocessor and CPU-peripheral connections compared to today’s systems that frequently use separate CPU and FPGA chips.

Most processors available for use inside FPGAs today offer limited performance or limited application software development ecosystems. For example, many FPGA users use Altera’s Nios or Xilinx’s MicroBlaze processors; Actel’s SmartFusion FPGA family embeds an ARM Cortex-M3. Perhaps the strongest processors integrated with an FPGA are the PowerPC cores in some of Xilinx’s Virtex products (which feature one or two PowerPC cores at a maximum of 550 MHz). In this architecture, the core is surrounded by a sea of programmable logic gates and connected via a non-standard bus architecture. This approach has achieved some acceptance, but apparently not enough: Xilinx will not develop it beyond the Virtex-5 FX products released in 2008.

Today, many system developers require a higher performance processor or a processor with better operating system, tool or software support than the options currently available in FPGAs. These developers typically select a processor chip targeted at their application area (for example, networking) and find a way to connect the processor to the FPGA, which is used to implement specialized compute engines and interfaces. Typical methods for connecting the CPU to the FPGA include using the CPU’s main memory bus with an SRAM-type interface, or using a high-speed serial interface designed for other purposes, such as PCI Express or SRIO. These approaches result in limited bandwidth and long latencies between the processor and the FPGA, which limits system performance. Compared to these systems, products built around Xilinx’s newly announced architecture should achieve smaller size, higher total performance, and lower power.

Xilinx seems to be thinking as much about the development flow as it is about the hardware. Specifically, Xilinx says it is working to target “software developers, who outnumber their hardware engineering counterparts by as much as 10:1.” To do so, Xilinx is working to define standards-based accelerators and peripherals, drivers and APIs that will help users “add functions to their designs with less assistance from their hardware design engineer counterparts.” Xilinx is collaborating with key vendors of C-to-FPGA synthesis flows in an effort to offer embedded software and system developers a way to take a function written in C for the processor and move it to the programmable logic fabric.

Xilinx says it will provide details on initial products based on the new architecture in early 2011, with samples available in late 2011. A development board using separate ARM and FPGA chips is available now.

Add new comment