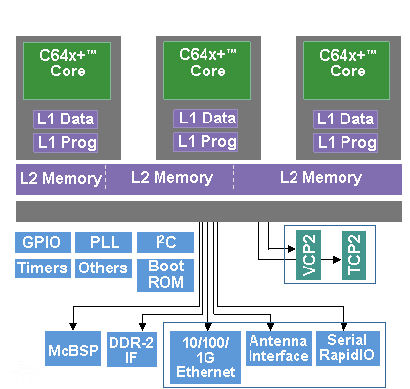

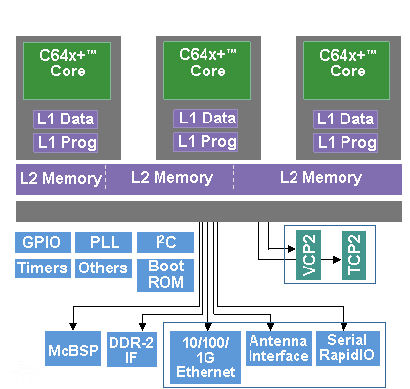

On October 14, 2008, Texas Instruments introduced a high-performance multi-core DSP, the TMS320C6474 that is intended for use in computationally demanding applications such as communications infrastructure, video surveillance, and medical imaging. The chip features three 1 GHz ‘C64x+ cores, each with its own L1 data and program cache, along with 3 MBytes of aggregate (not shared) L2 cache. As shown in Figure 1, the chip also contains a Viterbi accelerator and turbo-decoding accelerator along with a DDR interface, an antenna interface, an Ethernet port, and a McBSP serial port. The chip is fabbed in a 65 nm process and costs $225 in 1K quantities. TI is also offering an evaluation module that contains two ‘C6474 chips for $1,995.

Figure 1. Block diagram of Texas Instruments’ triple-core TMS320C6474. The antenna interface is a high-speed interconnect enabled by EMAC, AIF and SRIO SERDES interfaces. (Figure courtesy of TI)

The ‘C6474 is similar to the three-core TCI6487/8 chips that TI has been selling in its wireless infrastructure business. The new chip targets a broader range of applications (while still targeting comms infrastructure), particularly those that typically use a farm of DSPs. According to TI, the key advantages of using a single, three-core chip relative to using three separate ‘C64x chips are what you’d expect: lower power consumption, smaller footprint, and lower overall cost. According to TI, the migration to 65 nm enabled the company to squeeze the three cores into a chip that’s of comparable size to previous single-core 90 nm ‘C64x+ chips. TI says the new chip will consume about 6 watts and costs $261 in 100-unit quantities, which it compares to 9 watts and $744 for three ‘C6455 chips.

One difference to note though is that the ‘C6455 chips each contain their own Viterbi and turbo coprocessors. On the ‘C6474, there is only one of each decoder – so the chip’s performance on applications with heavy Viterbi or turbo decoding requirements may be lower than what you’d get with three separate chips. Similarly, the new chip has just one main memory interface, versus three if you use separate chips. So, one ‘C6474 is not quite equal to three ‘C6455’s.

The ‘C6474 will compete with (among other offerings) Freescale’s MSC8144, which was introduced back in 2006 and contains four 1 GHz SC3400 cores. Based on BDTI’s Communications Benchmark (OFDM) ™ results for the ‘8144 and TI’s 1 GHz single-core ‘C6455 it appears that the new three-core TI chip is likely to match or exceed the performance of the quad-core ‘8144 on this benchmark—at least in terms of the number of channels supported. But as we’ve written about before, extrapolating multi-core performance from single-core results is a tricky business; depending on the application, it can be hard to predict how application partitioning and resource contention will affect overall performance.

Because it’s targeting a wide range of high-performance applications, the TMS320C6474 will compete with many other high-performance processing technologies, including massively parallel processors from vendors such as Tilera and picoChip (both of which were recently benchmarked by BDTI) and IBM’s multicore Cell processor. Some of these chips are significantly more powerful than either the MSC8144 or the TMS320C6474 but TI has the advantage in developer familiarity and existing software; customers who are currently using banks of single-core ‘C64x+ chips can migrate fairly easily to the newer chip and reap significant size, power, and cost savings.

Add new comment