Fabless semiconductor start-up Percello, is hoping to find success in the UMTS (cellular) femtocell market by offering a highly integrated SoC for baseband processing. Today, femtocell baseband processing is typically handled by a combination of processors and FPGAs, but Percello believes that the potential for high volumes means that a cheaper, simpler solution is needed. The company’s initial product, the PRC6000 baseband chip, is designed to serve as a standalone femtocell processor and as a subsystem element for a residential gateway. The chip will be fabbed in a 65 nm process and tape-out is expected by the end of this year, with initial samples becoming available in the first quarter of 2009. Pricing has not been disclosed, though Percello claims that its chip price will be a key competitive advantage relative to DSP-plus-FPGA or SDR silicon-based solutions.

Percello is based in Israel and was founded in 1997 by former Modem-Art execs with expertise in developing ASICs for 3G handsets. The company has raised $18M in financing with Series B funding coming from T-Mobile.

The PRC6000 contains a 500 MHz MIPS24KC CPU to handle the upper layers of the UMTS stack and backhaul traffic, and has what Percello calls a “femtocell layer 1 engine (FLE)” that utilizes hardware accelerators to support UMTS Rel-7 WCDMA L1 functions along with MAC-hs and MAC-e functions (the latter two are the MAC functions used with the HSDPA and HSUPA protocols, respectively). The chip also incorporates a programmable CEVA TeakLite III DSP core to handle the L1 control functions. Percello says that its customers will not program the TeakLite processor themselves; instead, the company provides off-the-shelf software to implement all of the functionality up to the IUB interface.

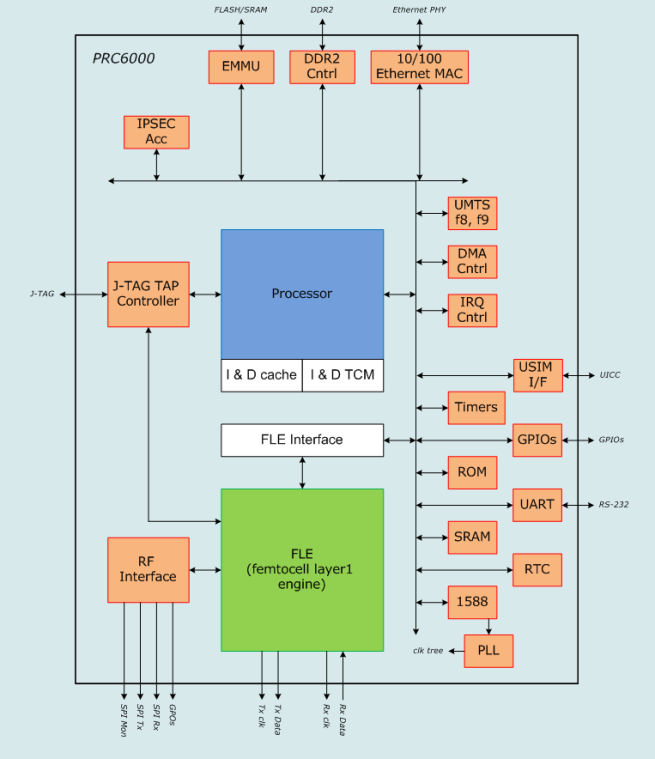

As shown in Figure 1, the PRC6000 also includes an extensive array of interfaces and peripherals, such as support for digital RF and USIM interfaces, 2G/3G sniffers, PTP/NTP accelerators, and IP-SEC accelerators. According to Percello, a single chip can handle eight calls, and higher capacity can be achieved by cascading chips.

Figure 1. PRC6000 block diagram (figure courtesy of Percello).

Percello’s biggest competition (at least initially) will come from picoChip, a fabless semiconductor vendor that offers massively parallel processors for picocell and femtocell processing. PicoChip has been heavily involved in femtocells and is already shipping chips into this market, though its current chips were originally marketed for picocell applications and are not specialized for femtocell. However, picoChip recently announced a new chip family, the PC30x, which is geared for femtocells and incorporates more specialized hardware and peripherals. The first member of that family, the PC302, supports up to four users. Another Israel-based company, DesignArt Networks, has also announced femtocell SoCs—but targets WiMAX femtocells rather than cellular.

Femtocells have the potential to become a high-volume market, so there is significant incentive for Percello and others to develop a highly specialized, lower-cost ASSP solution, particularly as the standards become more stable. The question is whether the femtocell market is ready for this transition now: it is difficult to predict when femtocells will begin shipping in high volumes. But it’s possible that the availability of cheaper chips will catapult the market into higher volumes. Percello is hoping that that’s what will happen, and it may well be making a good bet.

Add new comment