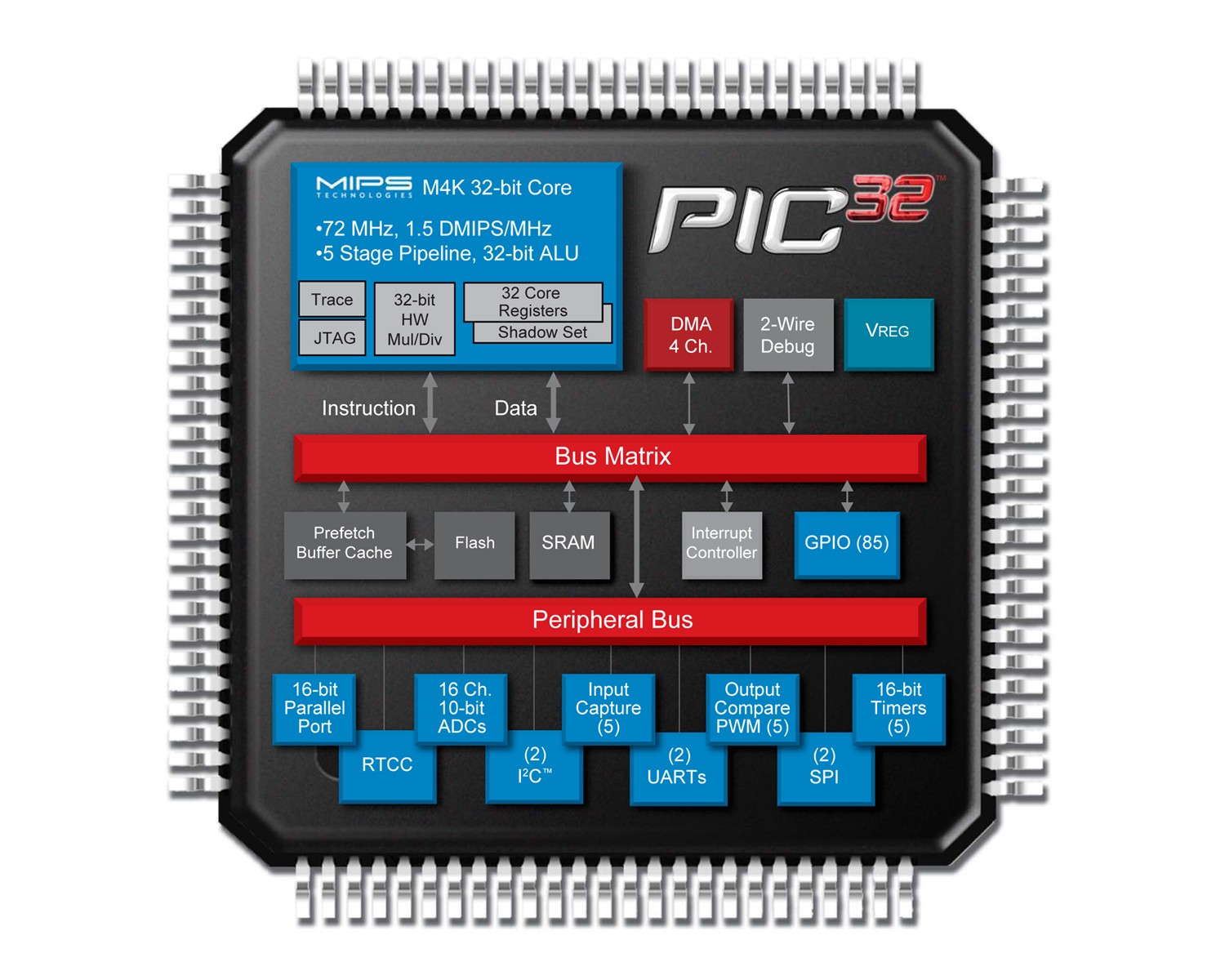

Last month, Microchip announced a new 32-bit microcontroller chip family, the PIC32. With this family, Microchip—a long-time player in 8- and 16-bit microcontrollers—is going after the 32-bit microcontroller market, and making a big change in architecture. Unlike Microchip’s earlier chips, which were based on the company’s proprietary processor architecture, the new family is based on the MIPS M4K core. PIC32 chips, which are currently sampling, will operate at up to 72 MHz, with pricing ranging from $2.95 to $5.30 in 10K quantities. A block diagram of the PIC32 is shown in Figure 1.

Figure 1. Block diagram of PIC32.

With the success of its previous products, it’s somewhat surprising that Microchip has switched horses now—but there are good reasons for doing so. It’s expensive to develop and maintain an in-house processor architecture, and it can be challenging to provide the full ecosystem—sophisticated tools, operating systems, reference designs, software libraries, etc.—that customers have come to expect. By going with a MIPS core, Microchip can leverage MIPS’ substantial resources and third-party support, while using its own existing peripheral libraries to create chips that are pin- and peripheral-compatible with earlier Microchip products (more on this later).

Of course, Microchip could have achieved the same effect by going with an ARM core (the relatively new Cortex-M3 springs to mind), which is what several of its competitors have done. According to Microchip, the company chose the M4K because it provided the best fit for deeply embedded applications—the best combination of power, performance, interrupt capabilities, code density, and potential future customizations. The M4K provides a co-processor interface, and also allows licensees like Microchip to define custom instructions. If Microchip decides to use custom instructions, however, they may compromise their ability to leverage some of the existing development infrastructure.

BDTI recently completed an evaluation of the MIPS M4K core, with a focus on assessing its signal processing features and capabilities. The M4K is not a DSP processor, but microcontrollers are increasingly called upon to do simple signal processing, so it’s useful to understand its capabilities in this area, and compare them to those of the Cortex-M3. Here are a few of the highlights of our evaluation.

The M4K core has more registers than the Cortex-M3 (32 vs. 16), and Microchip went one step further by configuring the core with an additional 32 shadow registers. More registers can mean more efficient software; they can be used, for example, to store more coefficients, parameters, and data values on-core, allowing instruction slots that would otherwise be needed for memory transfer operations to be used to increase the throughput of computation operations. But the Cortex-M3 has an advantage in multiplications—it can do single-cycle 32x32 multiplication, which the M4K cannot (it requires at least 2 cycles). The M4K can, however, do single-cycle 32x16-bit and 16x16-bit multiplies.

Compared to Microchip’s 16-bit, DSP-oriented dsPIC family, the PIC32 may be somewhat faster on typical DSP code. The newer chip can perform the same number of 16x16-bit multiplications per cycle (one) and executes at roughly twice the clock speed of current dsPIC chips. However, the dsPIC includes DSP-oriented features that the M4K lacks, such as support for saturation and rounding, hardware looping, and specialized address modes. Cumulatively, these features can have a significant impact on DSP performance—both in terms of speed and energy efficiency. It will be interesting to see whether Microchip ends up licensing a higher-performance MIPS core (such as the DSP-oriented 24KE) for future DSP-oriented chip families, or adding its own DSP-oriented custom instructions, as it did with the dsPIC.

In its press release, Microchip characterizes the PIC32 as being “software compatible” with its earlier chip families, but this characterization is slightly misleading. The chips are software compatible if you’re working in C (which Microchip expects most of its customers to do) but because the new chip family is based on a different instruction set architecture, any legacy assembly code will need to be rewritten.

The “software compatibility” Microchip is talking about is more of a system-level compatibility. Because the new chips use the same peripherals as the older chips, any C code written to use specific peripherals will work on the new chips, and Microchip provides peripheral libraries with compatible APIs. In addition, the new family is supported by the same tool chain (MPLAB) as all the other Microchip MCUs. In fact, according to Microchip, tool chain compatibility was another reason they chose the M4K; MIPS had placed the M4K compiler in the GNU compiler base, and Microchip was already using GCC for its 16-bit MCUS—thus making for an easier integration with Microchip’s existing tool chain.

Microchip’s decision to move to a licensable core—and to the M4K in particular—appears to be a reasonable one. Time will tell if Microchip’s customers will make the jump with them.

Add new comment