There’s no shortage of startup companies with massively parallel processor architectures targeting high-performance signal processing applications, but Israel-based newcomer Plurality (www.plurality.com) isn’t discouraged. The company recently introduced a new multi-core architecture, Hypercore, that can support from 16 to 256 RISC processors on a single chip. Plurality is betting that its patented “synchronizer/scheduler” hardware—which the company claims enables “the programmability of a serial processor”—will make Hypercore stand out from the crowd.

Hypercore targets real-time video processing, image rendering, software-defined radio, and packet processing, among other applications. Chips are expected to be available in the third quarter of 2007; no pricing has been disclosed. Initial Hypercore chips are expected to incorporate about 60 cores and run at 100 MHz in a 90nm process.

Hypercore is a MIMD (multiple instruction, multiple data) architecture based on an array of 32-bit RISC cores that implement the SPARC instruction set. To access these parallel resources, programmers must partition their applications by creating a “task map.” The task map lets the programmer identify parallelism in two ways. The first is by declaring a specific task as a “parallel” task, meaning that multiple, identical instances of this task can be replicated across multiple processors and run in parallel. The second is that the programmer can specify which tasks are dependent on each other and which aren’t—non-dependent tasks can be run in parallel on different processors. The task map is used as an input to the hardware synchronizer/scheduler, which dynamically maps tasks onto processors and tries to balance processor loading. Plurality provides a C compiler and assembler to create task code and a graphical debugger hooked to a cycle-accurate simulator for debugging.

Dynamic task allocation isn’t commonly used in embedded-oriented massively parallel multi-core chips, though it’s not unusual in chips used for other types of high-performance computing. Relative to static, compile-time task scheduling, dynamic scheduling may be able to achieve better hardware utilization in the face of dynamically varying workloads. But dynamic scheduling can introduce execution-time overhead as the chip (or operating system) figures out, on the fly, where to assign different tasks. Plurality asserts that its scheduling hardware introduces negligible overhead, though (for patent-related reasons) the company has not yet released a detailed explanation of its operation.

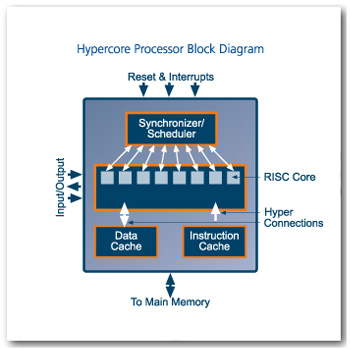

Hypercore is a symmetric multiprocessor based on a shared-memory model—as shown in the block diagram below, all of the cores are hooked up to the same data and instruction caches.

Figure 1. Block Diagram of Hypercore Architecture

Shared memory makes for easier programming (because it’s easier to keep data and tasks synchronized) but the resulting potential for memory contention can limit performance. For this reason, most massively parallel MIMD architectures (such as those from Ambric and PicoChip) use distributed memory. Plurality, however, claims that the Hypercore architecture can efficiently support up to 256 cores by virtue of a unique and efficient memory-sharing model. Because of patent considerations, Plurality hasn’t disclosed how this memory architecture works—but clearly, the effectiveness of this memory architecture will have an enormous impact on the success of the chip.

Usability is one of the key challenges for massively parallel architectures, and Plurality believes that its synchronizer/scheduler hardware and shared memory architecture provide the key to managing Hypercore’s complexity without degrading its performance potential. Plurality’s approach is interesting and unusual. How it will pay off should become clearer later this year, when Plurality samples its first chips.

Add new comment