In December Texas Instruments announced the TCI6487 multi-core baseband processor. The device will be manufactured in a 65 nm process and is intended mainly for GSM, TD-SCDMA and WiMAX basestation applications.

The TCI6487 features three TMS320C64x+ DSP cores running at 1 GHz. In comparison, its predecessor, the TCI6482, featured a single 1 GHz ‘64x+ core. TI has also added an antenna interface supporting OBSAI and CPRI protocols.

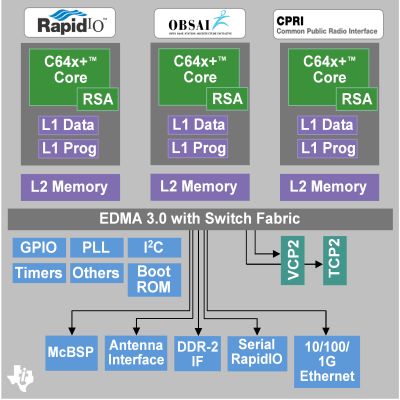

DSP cores in the TCI6487 communicate with each other and access shared resources by means of a non-blocking switch fabric and a semaphore hardware block. As shown in Figure 1, each ‘64x+ core features 32 KB of L1 program memory and 32 KB of L1 data memory, and uses a user-selected partition of the 3 MB of L2 SRAM/cache. The DSP cores in the TCI6487 include instruction-set extensions (dubbed “RSA” in Figure 1) to accelerate some CDMA processing tasks. In addition, the chip includes one Viterbi and one turbo decoding coprocessor. It also includes serial RapidIO (SRIO), Gigabit Ethernet, and DDR2 (667 MHz) interfaces.

Figure 1. Block diagram of the TCI6487

According to TI, the software-programmable TCI6487 is binary-compatible with TI’s previous ‘C64x and ‘C64x-based basestation chips; this will enable migration of legacy software. In addition, an optimized WiMAX software function library and historically strong tools support from TI are likely to make the TI chip attractive to system developers who wish to create their own WiMAX solutions.

The TCI6487 will face stiff competition, however. One notable competitor is Freescale’s MSC8144, containing four 1 GHz StarCore SC3400 DSP cores. BDTI has benchmarked the ‘64x+ and the SC3400 cores (both at 1 GHz) using the BDTI DSP Kernel Benchmarks™. BDTI has also estimated results for TI’s TMS320C6455 (which contains a single 1 GHz ‘64x+ core and a Viterbi coprocessor) and the MSC8144 on the BDTI Communications Benchmark (OFDM)™. Based on these results, BDTI estimates that the MSC8144 will provide noticeably higher throughput than the TCI6487 on general DSP-intensive tasks, but that the presence of the Viterbi coprocessor will give the TI device a slight capacity edge for typical basestation applications. TI has not disclosed pricing for the TCI6487, making cost/performance comparisons difficult. BDTI estimates that the TCI6487 would need to be priced at roughly $260 (quantity 1K) to give it equivalent cost/performance to the Freescale MSC8144 for typical baseband applications. (The MSC8144 is priced at $233 in 1K quantities.)

The new TI device will also compete with FPGAs. When implementing the BDTI Communications Benchmark (OFDM)™, high-end FPGAs from Altera and Xilinx were able to process many more channels and had much better cost/performance than high-end DSPs. (Analysis of these results appears in BDTI’s recent report, FPGAs for DSP.) BDTI estimates that high-end FPGAs will have a significant cost/performance advantage over the TCI6487 and other high-end DSPs on the types of applications represented by this benchmark. Adoption of FPGA-based approaches, however, will be limited by the much higher development effort associated with mapping applications onto FPGAs.

According to TI, the TCI6487 is currently sampling, with full production expected in the first quarter of 2007.

Add new comment