A methodology to demonstrate the design productivity of high-level synthesis tools

Program Benefits

The BDTI High-Level Synthesis Tool Certification Program (HLSTCP) enables tool vendors to:

- Attract customers and grow revenue through respected, independent analysis

- Accelerate the sales cycle by providing prospects with credible, detailed evidence of tool effectiveness

- Improve quality of results and usability via standardized, rigorous testing and feedback

Overview of Methodology

Background

As embedded processing applications have grown in complexity and embedded processing chips (CPUs, DSPs, FPGAs, and other types) have become more complex, there is an increasing need for more efficient application development methodologies. This is particularly true for FPGAs, massively parallel processors, and other non-traditional processing engines, which are inherently more complex than traditional single-core processors.

To address this need, many chip and tool companies have developed high-level application development tools. In this context, “high-level” means that the input to the tool is a design description largely independent of the details of the target processing engine. For example, C is a high-level language that is independent of the target processing engine; assembly language and register-transfer level (RTL) hardware description language (HDL) code are not.

High-level synthesis tools are of particular importance for FPGAs: the capacity and capabilities of FPGAs have expanded rapidly, but the ability of engineers to make effective use of FPGAs has not kept pace. In recent years a number of tool companies and FPGA suppliers have fielded high-level synthesis tools targeting FPGAs. These tools aim to boost productivity for FPGA designers, and in some cases to make FPGA design accessible to engineers who lack traditional hardware design skills (in particular, knowledge of RTL design). In addition to productivity gains for designs targeting a single hardware platform, high-level synthesis tools can greatly simplify retargeting a design to different FPGAs (from the same or from a different vendor) or even to an ASIC design. Anecdotal evidence suggests that some of these high-level synthesis tools may be very effective. However, prior to the introduction of the BDTI High-Level Synthesis Tool Certification Program there was virtually no credible, independent data or analysis that enabled prospective vendors to prove the effectiveness of their tools.

The BDTI High-Level Synthesis Tool Certification Program provides objective, credible data that enables tool vendors to prove the effectiveness of their tools, attract customer attention, and accelerate improvement of their tools.

Introduction to the Certification Program

The BDTI High-Level Synthesis Tool Certification Program provides credible, meaningful data and analysis evaluating the capabilities of high-level synthesis tools used with FPGAs. The program focuses on two main aspects of these tools:

- Quality of results (performance and efficiency of the synthesized design)

- Usability (designer productivity and ease-of-use)

The program evaluates the performance of high-level synthesis tools when used to develop demanding, highly parallelizable real-time digital signal processing applications, since such applications are a primary target market for FPGAs. The program compares the quality of results and usability (productivity and ease-of-use) of high-level synthesis tool flows with two well-known alternatives:

- A mainstream DSP processor used with its associated software development tool chain

- An FPGA used with traditional hand-written RTL and RTL-based tool chains

Note that high-level synthesis tools are used together with traditional RTL, HDL-based FPGA design tools: the high-level synthesis tool generates an RTL design, and traditional FPGA tools are used for synthesis, placement, and other necessary steps to obtain a complete FPGA implementation of an application. For this reason, the BDTI High-Level Synthesis Tool Certification Program evaluates high-level synthesis tools used in combination with FPGA RTL tools.

Target Platforms

The program uses the Xilinx Spartan-3A DSP FPGA combined with Xilinx ISE and EDK tools, and the Xilinx XtremeDSP Video Starter Kit. Spartan-3A DSP FPGAs are based on Xilinx’s low-cost Spartan-3A family, but have a number of enhancements to accelerate digital signal processing.

The target DSP platform is a Texas Instruments TMS320DM6437 DSP processor, programmed using TI Code Composer Studio tools, and the TI Digital Video Evaluation Module. The Texas Instruments TMS320DM6437 includes a 594 MHz TMS320C64x+ DSP core along with a video processing subsystem (i.e., video hardware accelerators). The hardware accelerators are not of benefit in implementing the program workloads and were not used by BDTI.

FPGA Design Using High-Level Tools

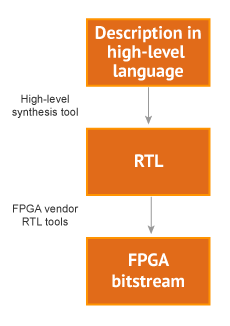

Figure 1: Design Flow Using High-Level Synthesis Tools with FPGA Vendor RTL Tools

Unlike a DSP tool flow, where a single integrated tool chain (in our case, TI Code Composer) is used throughout the entire design process, multiple tool flows are required to complete an end-to-end FPGA design. The typical implementation process for an FPGA-based design using a high-level synthesis tool is shown in the block diagram in Figure 1.

Since the high-level synthesis tool is only used in the first step (to create RTL from a description in high level language), BDTI could have limited evaluation to this portion of the implementation process. However, potential users need to understand how to get from a description of the application in a high level language all the way to an FPGA—which requires the use of FPGA vendor-specific RTL tools. Because of this, BDTI evaluates the entire process shown in Figure 1, including the FPGA vendor RTL tools.

Evaluation Workloads

BDTI uses two evaluation workloads (example applications) in the program:

- The primary workload, the BDTI Optical Flow™ Workload, is an optical flow (video motion analysis) application

- The second workload, the BDTI DQPSK Receiver™ Workload, is a wireless communications receiver baseband application

The BDTI Optical Flow Workload is used to enable comparisons between:

- An FPGA implementation developed using the high-level synthesis tool in conjunction with Xilinx RTL tools

- A TI DSP processor implementation developed using the associated software development tool chain

The BDTI DQPSK Receiver Workload is used to enable comparisons between:

- An FPGA design developed using the high-level synthesis tool in conjunction with Xilinx RTL tools

- Traditional RTL design techniques targeting the same FPGA using the Xilinx RTL tools

These workloads have been designed to be broadly representative of the types of embedded computing applications that electronic system designers implement using FPGAs. They have been designed to be sufficiently complex to be realistic, but simple enough to be practical for use in this program.

Obtaining BDTI Certified™ Results

Program Participation

High-level synthesis tool vendors may participate in the BDTI High-Level Synthesis Tool Certification Program at one or more levels.

Licensing

First, the vendor must license the program specifications from BDTI. A license to the program provides:

- Specifications to the BDTI High-Level Synthesis Tool Certification Program, including:

- Detailed written specifications for implementation of the workloads

- Reference implementation of the workloads in a high level language

- Test vectors for verifying the functionality of workload implementations

- Training

- Technical support

Vendor Self-Evaluation

As the second step, a vendor may perform a self-evaluation by implementing the workloads and comparing its results with those published by BDTI and other vendors. Results from a self-evaluation may be used internally to improve technology and understand product strengths and weaknesses.

Certification and Analysis

Finally, a vendor may have its results certified by BDTI. Certification is necessary to disclose results to third parties. During certification and analysis, BDTI uses the tool in depth to assess its capabilities and usability and validates the results obtained by the vendor in the self-evaluation.

Participate in the Program

To participate in the program or to get details of licensing and certification, contact BDTI by phone at +1 925 954 1411 or via the web.

Current Results

To see results please visit the BDTI High-Level Synthesis Tool Certification Program Results page.