Optimized DSP Software • Independent DSP Analysis

# Evaluating the Latest DSPs for Communications Infrastructure Applications

Berkeley Design Technology, Inc. 2107 Dwight Way, Second Floor Berkeley, California 94704 USA +1 (510) 665-1600

> info@BDTI.com http://www.BDTI.com

© 2002 Berkeley Design Technology, Inc.

# **Processor Requirements**

Communications Infrastructure Equipment

### Key criteria

- Board area per channel

- Power per channel

- Cost per channel

- Large-system integration support

- Tools

- Application-development infrastructure

- Architecture roadmap

© 2002 Berkeley Design Technology, Inc.

2

© 2002 Berkeley Design Technology, Inc.

#### **Evaluating the Latest DSPs for Communications Infrastructure Applications**

© 2002 Berkeley Design Technology, Inc.

© 2002 Berkeley Design Technology, Inc.

© 2002 Berkeley Design Technology, Inc.

#### **Evaluating the Latest DSPs for Communications Infrastructure Applications**

# &DTi

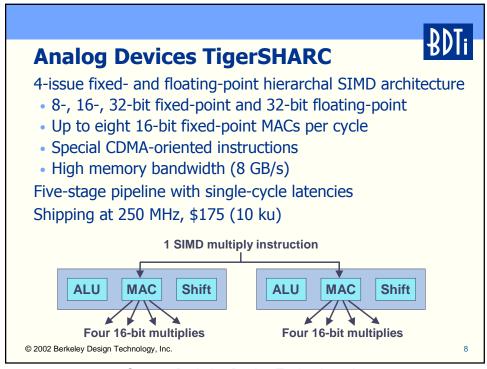

## **Analog Devices TigerSHARC**

Strengths and Weaknesses

- \*Speed rivals fastest fixed- and floating-point DSPs\*

- ↓ Poor cost-performance\*

- ↓Two-level SIMD complicates programming

- †Sophisticated memory system

- † Leading memory bandwidth

- † Excellent multiprocessor support

- **†**Good tools

- ↓ But limited third-party support

- ↓Uncertain roadmap

- ↓ Only one chip announced so far

- ↓ Can ADI support all of its new architectures?

© 2002 Berkeley Design Technology, Inc.

\*Based on architectural comparisons

9

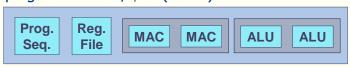

# **LSI Logic ZSP400**

A 4-Way Superscalar DSP Core

4-issue 16-bit fixed-point superscalar architecture

- Up to two 16-bit MACs per cycle

- ALUs also function as AGUs, shifters

- Good support for 32-bit operations

Five-stage pipeline with single-cycle latencies 16-bit instruction set with no conditional execution Available as core, ASIC library component, ASSP,... Compatible with higher-performance ZSP G2 Shipping at 200 MHz, \$36 (10 ku)

© 2002 Berkeley Design Technology, Inc.

10

© 2002 Berkeley Design Technology, Inc.

## **Conclusions**

Developers of communications infrastructure equipment have many choices of processors.

There is no "ideal" processor:

- Any choice brings trade-offs

- The "best" processor depends on the details of the application

Performance and efficiency are key:

Be wary of vendor hype; use reliable benchmarks

Factors other than performance are also critical:

- · Vendors' roadmaps, business plans, etc.

- Tools and third-party support

© 2002 Berkeley Design Technology, Inc.

12

© 2002 Berkeley Design Technology, Inc.