Insight, Analysis, and Advice on Signal Processing Technology

# **Processors for Consumer Audio/Video Applications**

(Class CSD-620)

Berkeley Design Technology, Inc.

info@BDTI.com http://www.BDTI.com

© 2005 Berkeley Design Technology, Inc.

## **Outline**

- Motivation and scope

- Challenges

- Application requirements

- Processor architecture options

- Selection methodology

- Conclusions

© 2005 Berkeley Design Technology, Inc.

### **Motivation**

- Technology creates new opportunities, e.g.,

- Broadband Internet enables video on demand

- Product convergence: cellphone+camera, digital still+video camera

- "Right" processor key to product success

- Supports, enables desired product features

- Heavily influences product cost, power consumption, performance (end user experience)

- Can simplify development effort and cost

- Range of processor options is large and rapidly changing, making selection difficult

© 2005 Berkeley Design Technology, Inc.

3

# Scope

- Processor selection for consumer media products with varying features:

- Application a mix of audio, video, or still image

- MP3 players, voice recorders, cell phones

- · Still or video cameras, set-top boxes

- Using streaming or stored content

- Battery or line powered, portable or fixed

- Cost constrained

- Input/output quality varies by application

- E.g., lower quality audio for voice recorder, high quality audio for MP3 or DTS playback

© 2005 Berkeley Design Technology, Inc.

4

### **Outline**

- Motivation and scope

- Challenges

- Application requirements

- Processor architecture options

- Selection methodology

- Conclusions

© 2005 Berkeley Design Technology, Inc.

5

# **Processor Selection Challenges**

The fundamental problem:

- Many processors and types of processors to choose from

- Complex processors, applications

- · Multiple standards to support

- Many important selection criteria to consider

- Unpredictable changes in processor options, application requirements

- · Poor information, complex analysis

- · Limited time and resources for selection

The wrong choice can be fatal for a product development effort

© 2005 Berkeley Design Technology, Inc.

6

### **Outline**

- Motivation and scope

- Challenges

- Application requirements

- Processor architecture options

- Selection methodology

- Conclusions

© 2005 Berkeley Design Technology, Inc.

7

# **Player/DRM Requirements**

- Manages other application sub-modules (e.g., codecs), provides user interface

- Processing requirements: 1's-10's MIPS

- Good tools are critical

- Processor features that benefit compilers are useful, e.g.,

- · Orthogonal instruction set

- Large, linear address spaces

- Flexible data type support

- I/O bandwidth requirements depend on:

- Application features, peripheral mix

- Software architecture

© 2005 Berkeley Design Technology, Inc.

8

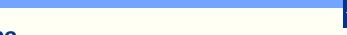

# **BDT**i

# **I/O Requirements**

- Processors must support multiple I/O interface standards both internal and external

- Basic in-system serial & parallel (CCD, I2S, SPI, "host port")

- Storage ports (glueless SDRAM, ATA, flash)

- External connectivity (Ethernet, USB, 1394, wireless)

- Support for high transfer rates

- Video data rates range from 100's—1000's KB/s

- Autonomous, intelligent I/O

- E.g., programmable communications co-processors reduce load on core processor

© 2005 Berkeley Design Technology, Inc.

10

# **Development Effort and Cost**

- Development effort affected by many factors

- Programming model complexity

- More powerful processor → more complex model

- More complex model  $\rightarrow$  increased development effort

- Don't overlook complexity of intelligent I/O

- Availability of off-the-shelf software components

- Codecs

- OSs

- Device drivers

- Reference designs

- · Quality of tools

- Maturity, capability of development tools

- Support for I/O in debug

- The right choice of processor can reduce development effort and cost

© 2005 Berkeley Design Technology, Inc.

11

# **Outline**

- Motivation and scope

- Challenges

- Application requirements

- Processor architecture options

- Selection methodology

- Conclusions

© 2005 Berkeley Design Technology, Inc.

12

| I B                                              |          |    |

|--------------------------------------------------|----------|----|

| leo Processor Types                              |          |    |

| Processor Type                                   | Chips    | IP |

| PC CPU                                           | ✓        |    |

| RISC CPU                                         | ✓        | ✓  |

| DSP (generic or specialized)                     | ✓        | ✓  |

| Media processor, heterogeneous multiprocessor    | <b>√</b> |    |

| Customizable processor                           |          | ✓  |

| ASIP                                             |          | ✓  |

| Reconfigurable processor                         | ✓        | ✓  |

| FPGA                                             | ✓        |    |

| Fixed-function engines                           | ✓        | ✓  |

| ASSP (incorporating one or more processor types) | <b>√</b> |    |

© 2005 Berkeley Design Technology, Inc.

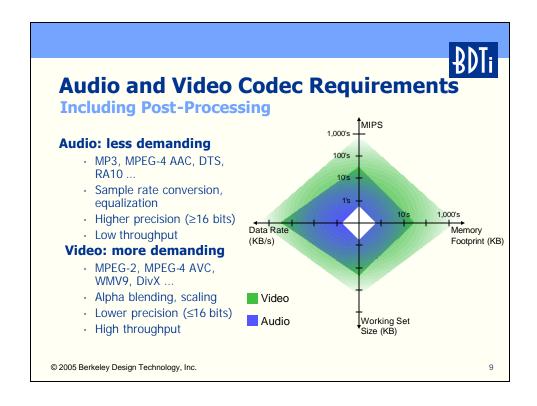

### **ASSPs**

# BDTi

### **Strengths and Weaknesses**

- ◆Often very well matched to the application

- ◆SoCs with extensive integration

- ◆Architecture tuned for the application

- ↑Can yield excellent performance, cost, energy efficiency

- **↑**Ease of use

- ♠ Reduce system development costs

- ♠ Reduce required implementation expertise

- Often inflexible

- Limited differentiation opportunities for system designer

- Usually single-source

- Roadmap often unclear

© 2005 Berkeley Design Technology, Inc.

15

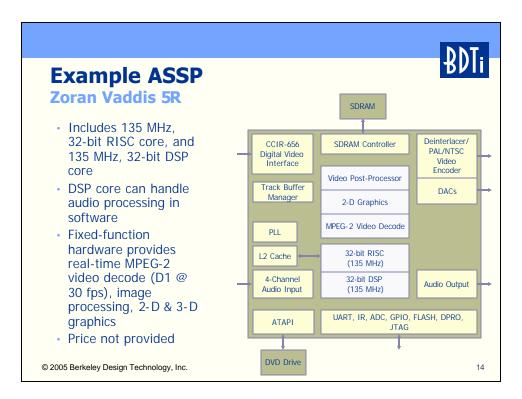

### **FPGAs**

### **Strengths and Weaknesses**

- ↑Massive performance gains over instruction set processors on some DSP tasks

- ♠Adjust data widths throughout algorithm

- → Huge throughput, cost/performance advantages over DSP, general-purpose processors in some applications

- ♠ Architectural flexibility can yield efficiency

- ↑ Adjust data widths throughout algorithm

- ♠ Parallelism where you need it; distributed storage

- Dynamic reconfigurability?

- High development effort compared to instruction-set processors

- Complex design flow is unfamiliar to most signal-processing engineers

- Suitability for single-channel, low-power, costsensitive signal-processing applications not proven

© 2005 Berkeley Design Technology, Inc.

17

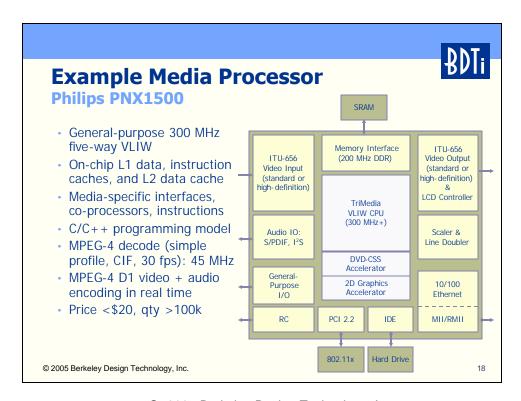

### **Media Processors**

### **Strengths and Weaknesses**

- Higher performance than most DSPs, GPPs

- ◆ VLIW, huge register sets, wide SIMD typical

- ◆ High performance peripherals, co-processors

- Very complex programming models

- Better support for media processing in development tools, infrastructure, compared to GPPs

- Application performance compiler-dependent

- Compilers can be poor quality

- Maturing technology—but roadmaps unclear

- 3<sup>rd</sup> party support weaker than other processor types

- Development cost, risk, lower than ASIC, FPGA

© 2005 Berkeley Design Technology, Inc.

19

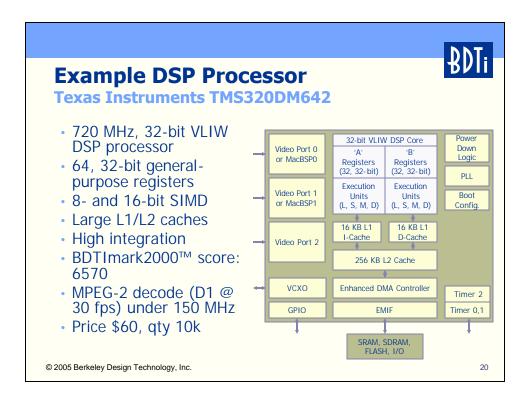

### **DSP Processors**

### **Strengths and Weaknesses**

- Performance, efficiency on media applications vs. general-purpose processors

- But not as strong as customized solutions, and may not be adequate for demanding tasks

- ↑ Media-oriented development tools, infrastructure

- Tools not as sophisticated as those available for general-purpose processors

- Often, poor compiler quality

- ◆ Stable, mature technology and vendors

- Third-party audio/video application software available

- Support for non-DSP software not as strong as, e.g., RISC

- Relatively low development cost, risk

© 2005 Berkeley Design Technology, Inc.

21

#### **Example Embedded RISC CPU Intel PXA255** · 400 MHz, 32-bit RISC with 2 KB Mini D\$ RTC modest DSP extensions Power Mar SDRAM Ctrl Timer/PWM 32 KB 32 KB BDTImark2000™ score: 930 Clock Ctrl MPEG-4 decode (simple) AC97 profile, CIF @ 30 fps) 200 Interrupt Ctrl 125 **XScale** SRAM Control I<sup>2</sup>C • 16-bit SIMD, 32-bit data types benefit media apps IrDA/UART Burst Flash Predicated instruction SSP/SPI/ uWire execution good for control MMC/SD Variable Good development tool Latency I/O HART support, optimized DSP software available (e.g., PCMCIA/CF Bluetooth UART Card Control Intel IPP), good OS options USB 1.1 Price \$35, qty 10k (2004) JTAG DMA Color LCD Controller Master I/F pricing) © 2005 Berkeley Design Technology, Inc. 22

## **Embedded RISC CPUs**

### **Strengths and Weaknesses**

- → Can have adequate performance on media applications

- Often less efficient that DSPs and media processors

- Dynamic features complicate programming

- Complicates optimization & ensuring real-time

- Sometimes, convoluted programming model

- - ♠ E.g., TCP/IP network stacks

- ↑ Multi-vendor architectures more common

- Good tools, but generally weak on support for media application development

- ◆ Very good third-party OS, software component support

- ◆ Compatibility more common

- High integration parts increasingly common

© 2005 Berkeley Design Technology, Inc.

23

### **Example PC CPU VIA Technologies C3** 1 GHz x86 compatible Moderate power consumption, cost SSE support for media applications, supports fixed-, floating-point types Access to massive x86 3<sup>rd</sup>party software, tools base Familiar to software, hardware developers MPEG-4 decode (D1, 30 fps) using 35% of CPU, when using VIA CN400 chipset CPU: \$70, chipset: \$23 (qty 10k) Image © VIA Technologies © 2005 Berkeley Design Technology, Inc. 24

# PC CPUs (GPPs)

### **Strengths and Weaknesses**

- ◆ Can handle complex media processing tasks

- ◆ May be as fast or faster than DSPs...

- ... but cost & power consumption typically higher

- Dynamic features complicate optimization, real-time design

- Generally weak on integration

- ↑ Many options for OS, 3rd party application software

- ◆ Easier migration of PC applications

- ♠ Excellent targets for non-signal-processing tasks

- ♠ E.g., protocol stacks

- ◆ Compatibility, multi-vendor architectures common

- ◆ Development tools mature, powerful

- But typically lack features useful for media application development

© 2005 Berkeley Design Technology, Inc.

25

# **Outline**

- Motivation and scope

- Challenges

- Application requirements

- Processor architecture options

- Selection methodology

- Conclusions

© 2005 Berkeley Design Technology, Inc.

26

# **Processor Selection Methodology**

Use a hierarchical approach to make the problem manageable:

- Determine selection criteria

- Prioritize or assign weights to selection criteria

- Use critical criteria to eliminate obviously unsuitable choices

- · Begin with classes of processors

- Evaluate and rank candidates

- · Weigh trade-offs among non-critical criteria

- Iterate as necessary

- · Refine criteria and analysis of candidates

© 2005 Berkeley Design Technology, Inc.

27

# **Processor Selection Criteria**

**Signal-Processing-Centric Concerns**

- Performance on relevant audio/video tasks

- Speed

- Memory bandwidth: on-chip, off-chip

- Execution-time predictability

- Dynamic features confound determinism

- Energy consumption

- Fixed-point vs. floating-point

- · Floating-point less important for video

- Data word size(s)

- Memory usage

© 2005 Berkeley Design Technology, Inc.

28

### **Processor Selection Criteria**

**Signal-Processing-Centric Concerns**

- On-chip integration

- Memory, peripherals, I/O interfaces, coprocessors

- Development effort, risk

- Media-oriented tools, infrastructure

- Programming model complexity

- Application software components

- Reference designs

- Tools, support (vendor, 3<sup>rd</sup> party)

- · Accurate cycle-count and memory profiling

- · Visibility into cache, pipeline

- Features useful for integration, real-time testing

- · E.g., on-chip debug support

© 2005 Berkeley Design Technology, Inc.

29

## **Processor Selection Criteria**

**General Concerns**

- Cost

- Packaging options

- Roadmap

- Availability; reliability of supply

- Multi-vendor architectures a plus

- New spins, new architectures, compatibility

- Core version available?

- Special requirements

- Variable-voltage operation

© 2005 Berkeley Design Technology, Inc.

30

# **Assessing Performance**

- Use results from relevant application modules

- More accurate than kernel benchmark mapping—if available

- Use caution! The data may be misleading or incomplete

- Use kernel benchmarks & application profiles

- Useful when application data isn't available

- Use kernel benchmark results to predict application module performance

- Use care with either approach

- · Hazards include data types, multitasking effects ...

© 2005 Berkeley Design Technology, Inc.

31

# **Assessing Performance, continued**

- Core CPU performance isn't enough

- Must also consider memory sizes and bandwidths

- I/O bandwidths and overheads: data movement can be very costly

- Impact of software partitioning in multiprocessor systems

- Must refine software architecture to predict performance

- Dynamic features complicate performance prediction

- Assessing energy efficiency can be very difficult

© 2005 Berkeley Design Technology, Inc.

# **Development Considerations**

- Language support

- Quality of C compiler; availability of C++ compiler

- Support for assembly language optimization

- Software availability

- Media processing components

- · Player, device drivers, operating system

- Hardware/software reference designs

- Debug/development benefit from tools with:

- Peripheral and multi-processor simulation

- · Non-intrusive, real-time debug

- Compatibility, developer familiarity

© 2005 Berkeley Design Technology, Inc.

33

# **Availability and Roadmap**

- Risk

- Is the chip available in volume today?

- Are there second sources of the chip or compatible chips?

- What does the errata list look like?

- Roadmap

- What is the vendor's commitment to evolving the chip? E.g., improved integration, reduce cost

- What is the vendor's roadmap for next-generation chips? Compatibility?

- What is your confidence that the vendor will execute on its roadmap?

© 2005 Berkeley Design Technology, Inc.

### **Outline**

- Motivation and scope

- Challenges

- Application requirements

- Processor architecture options

- Selection methodology

- Conclusions

© 2005 Berkeley Design Technology, Inc.

35

# 80

## **Conclusions**

- Choosing a processor for a consumer media product is easy

- Choosing the best processor for your particular product is hard

- Vast range of options

- Many complex, competing criteria to consider

- Poor information

- Fast changing requirements and options

- Limited time and resources

© 2005 Berkeley Design Technology, Inc.

36

# Conclusions, cont.

- Use a hierarchical approach

- Develop a well-defined hierarchy of product requirements

- Start with the critical criteria and iteratively narrow the field

- Expect to make trade-offs

- Assessing performance is a challenge

- Resource-hungry algorithms, cost-constrained processors, many variables

- Development-related considerations are key

- Appropriate integration is essential to low system cost

© 2005 Berkeley Design Technology, Inc.

37

## **Trends: Processors**

- Consumer media applications are becoming a major focus of processor vendors

- · Expect more competitors, more options

- Technology, competition pushes performance up; price and power consumption down

- Enabling new types of products, new levels of functionality

- But not all processors are well matched to media processing workloads

- Increasing architectural complexity

- Many heterogeneous multiprocessors

- Integration increasing

- Development infrastructure is a key differentiator

© 2005 Berkeley Design Technology, Inc.

# **Trends: Development**

- Products are becoming more complex

- · Stereo receiver vs. home media center

- Processors are becoming more complex

- Algorithms are becoming more demanding

- Nobody knows which ones will dominate

- Optimization continues to be essential

- Huge processor-to-processor differences in development infrastructure

- Support for media applications

- Off-the-shelf, optimized software components increasingly important

© 2005 Berkeley Design Technology, Inc.

39

# For More Information... www.BDTI.com

Inside [DSP] newsletter and quarterly reports Benchmark scores for dozens of processors Pocket Guide to Processors for DSP

Basic stats on over 40 processors

Articles, white papers, and presentation slides

- Processor architectures and performance

- Signal processing applications

- Signal processing software optimization comp.dsp FAQ

© 2005 Berkeley Design Technology, Inc.

40