Insight, Analysis, and Advice on Signal Processing Technology

# Microprocessors vs. DSPs: Fundamentals and Distinctions

(DSP-502)

Kenton Williston Berkeley Design Technology, Inc.

> info@BDTI.com http://www.BDTI.com

© 2005 Berkeley Design Technology, Inc.

## **Workshop Outline**

- Definitions

- DSP Algorithms Shape DSPs

- Comparing DSPs and GPPs

- Comparing Performance

- · When to Use Which

- Conclusions

© 2005 Berkeley Design Technology, Inc.

2

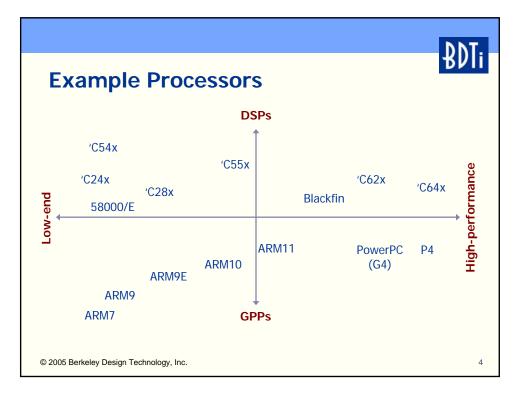

## **Definitions**

#### Microprocessors—General-Purpose Processors (GPPs)

- CPUs for PCs and workstations

- E.g., Intel Pentium III

- 32-bit GPPs for embedded applications

- E.g., ARM ARM7

#### Digital Signal Processors (DSPs)

Microprocessors specialized for signal processing applications

#### Low-end DSPs and GPPs

Architectures targeting extremely cost sensitive markets, often older architectures

#### High Performance DSPs and GPPs

- Architectures that use advanced techniques to improve parallelism, performance

- Usually have higher clock rates

© 2005 Berkeley Design Technology, Inc.

3

© 2005 Berkeley Design Technology, Inc.

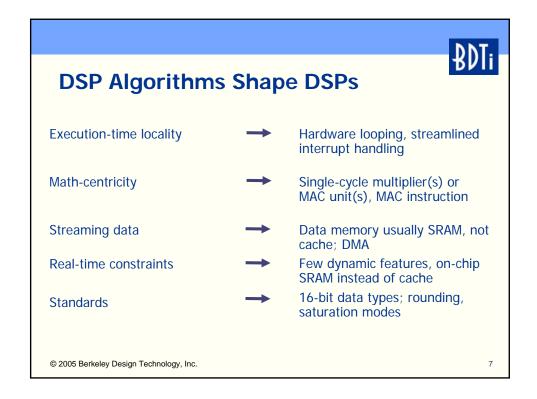

## **DSP Algorithms Shape DSPs**

**How Signal Processing is Different From Other Tasks**

- Very computationally demanding

- Requires attention to numeric fidelity

- High memory bandwidth requirements

- Streaming data—and lots of it

- Predictable data access patterns

- Execution-time locality

- Math-centric

- Real-time constraints

- Standards: algorithms, interfaces

© 2005 Berkeley Design Technology, Inc.

5

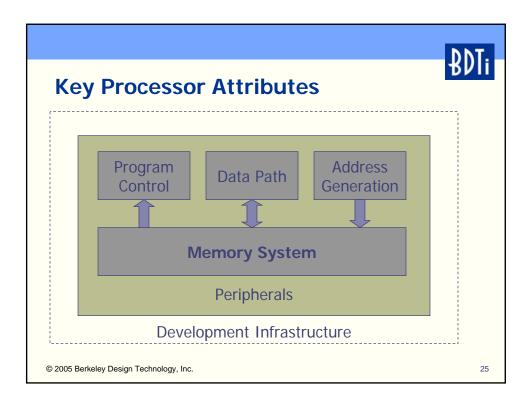

## **DSP Algorithms Shape DSPs**

Computational demands

Multiple parallel execution units, hardware acceleration of common DSP functions

Numeric fidelity

Accumulator registers, guard bits, saturation hardware

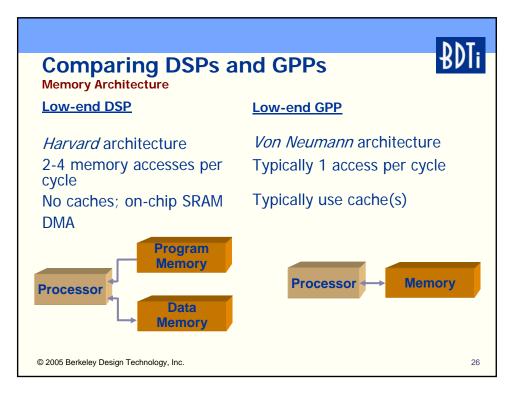

High memory bandwidth

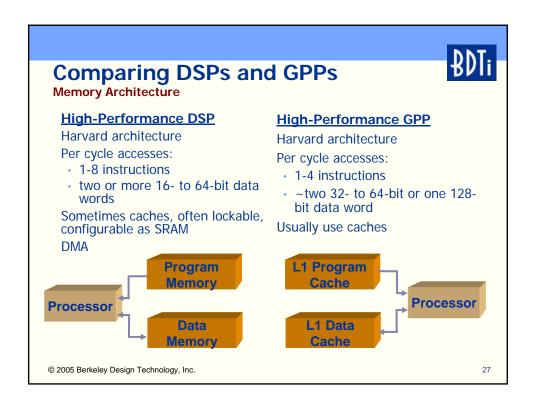

Harvard architecture, support for parallel moves

Predictable data access patterns -

Specialized addressing modes, e.g., modulo, bit-reversed

© 2005 Berkeley Design Technology, Inc.

6

## BD

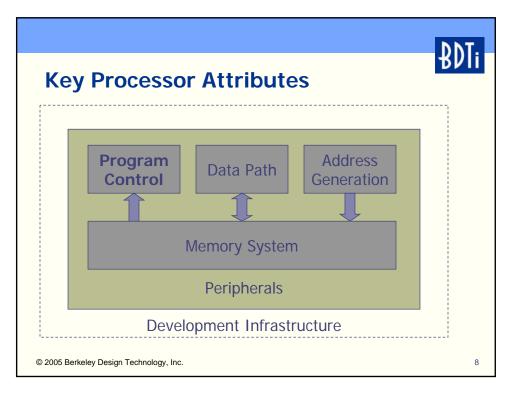

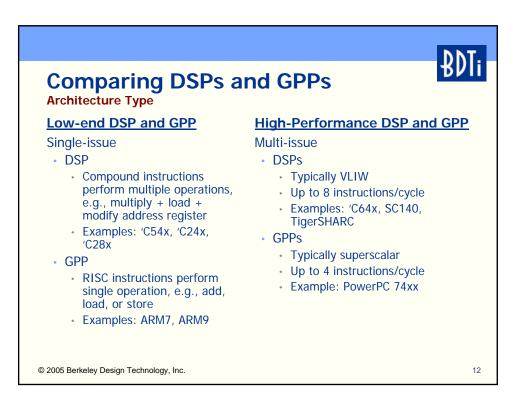

## **Comparing DSPs and GPPs**

Instruction Set

**Low-end DSP**

Specialized, complex

instructions

Multiple operations per

instruction

Poor orthogonality

**Low-end GPP**

General-purpose instructions

Typically only one

operation per instruction

Good orthogonality

mac x0,y0,a x:(r0)+,x0 y:(r4)+,y0

mpy r2,r3,r4 add r4,r5,r5 mov (r0),r2 mov (r1),r3 inc r0

inc r1

© 2005 Berkeley Design Technology, Inc.

9

## **Comparing DSPs and GPPs**

**Instruction Set**

**High-Performance DSP**

Simple to moderatelycomplex instructions

Moderate to excellent

orthogonality

**High-Performance GPP**

Baseline:

Simple instructions

Moderate to excellent

orthogonality

With SIMD extensions:

Moderately complex

instructions

Moderate to excellent

orthogonality

© 2005 Berkeley Design Technology, Inc.

10

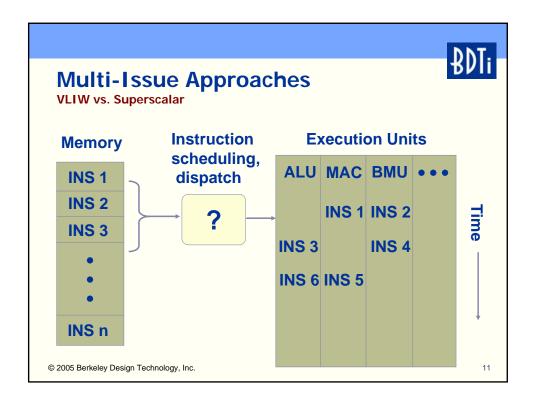

Trade-Offs: Superscalar vs. VLIW

Superscalar (high-performance GPPs, mostly)

- Increased hardware complexity

- · Silicon area, power consumption

- Dynamic behavior

- · Complex performance model, timing variability

- Increased performance with binary compatibility

- Decreased software complexity (programmer/compiler)

### VLIW (high-performance DSPs, mostly)

- Decreased hardware complexity

- No dynamic behavior

- Binary compatibility difficult (downward direction)

- · Increased software complexity

© 2005 Berkeley Design Technology, Inc.

13

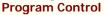

## **Comparing DSPs and GPPs**

#### **Low-end DSP**

Hardware looping

Interrupts disabled during certain operations

Limited or no register shadowing

Simple pipelines

Often provide delay slots to hide branch latencies

May support fast interrupts

#### **Low-end GPP**

Software looping

Interrupts rarely disabled

Register shadowing common

#### Simple pipelines

No delay slots or branch prediction

May support fast interrupts

© 2005 Berkeley Design Technology, Inc.

14

**Program Control**

#### **High-end DSP**

Usually support hardware looping

Interrupts rarely disabled May offer shadow registers Complicated pipelines in some cases

- May be non-interlocked

- May have multi-cycle latencies

- May use branch prediction

May support fast interrupts

#### **High-end GPP**

Software looping

Interrupts rarely disabled Register shadowing common Moderately to extremely complicated pipelines

- May have very long instruction latencies

- Often use branch prediction

May support fast interrupts

© 2005 Berkeley Design Technology, Inc.

15

## **Comparing DSPs and GPPs**

**Branch Prediction: Strengths and Weaknesses**

In many applications, branch prediction is very accurate

This includes signal processing applications, where most branches are part of for-next loops

Complex branch prediction algorithms introduce timing uncertainty

It can be difficult to predict whether the prediction will be correct at any given instant

© 2005 Berkeley Design Technology, Inc.

16

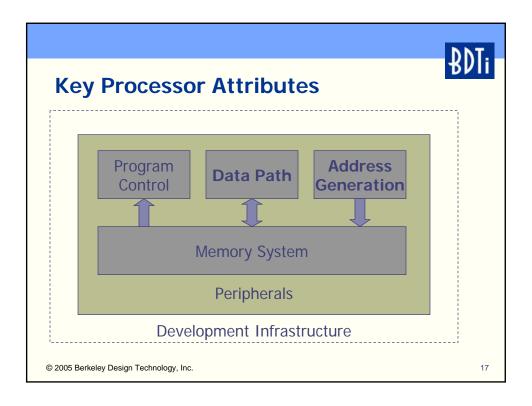

**Data Path**

#### **High-Performance DSP**

Up to 8 arithmetic units

## Some specialized arithmetic units

• E.g., MAC unit, Viterbi unit

Support multiple data sizes Limited to excellent bitmanipulation capabilities Hardware support for managing numeric fidelity

© 2005 Berkeley Design Technology, Inc.

#### **High-Performance GPP**

1-3 arithmetic units

## General-purpose arithmetic units

E.g., integer unit, floatingpoint unit

### Support multiple data sizes

May have superior bitmanipulation capabilities

Saturation, rounding typically take extra cycles

19

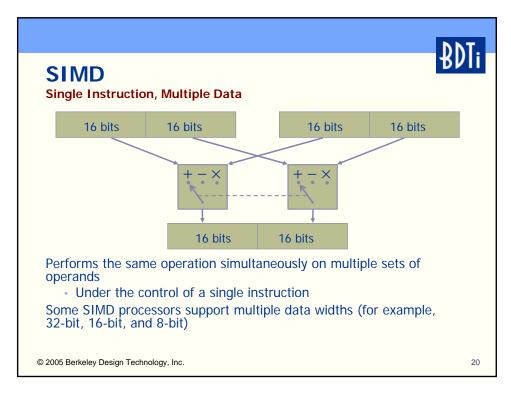

**SIMD Features**

**Low-end DSP and GPP**

**High-Performance DSP and GPP**

Very limited SIMD features in low-end DSP

E.g., dual add, subtract of 16-bit fixed-point data

Limited to extensive SIMD features in high-end DSPs

- E.g., TigerSHARC

- 4 x 32-bit float

- 4 x 32-bit integer

- 8 x 16-bit integer

- 16 x 8-bit integer

No SIMD support in lowend GPP

Extensive SIMD features in highend GPPs

- E.g., PowerPC 74xx

- 4 x 32-bit float

- 4 x 32-bit integer

- 8 x 16-bit integer 16 x 8-bit integer

© 2005 Berkeley Design Technology, Inc.

21

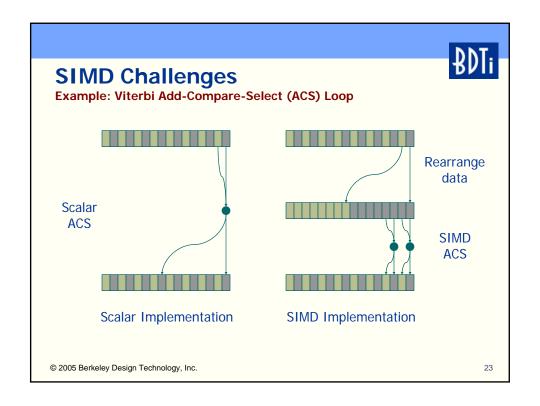

## **SIMD Challenges**

Each instruction performs lots of work

Data parallelism

Algorithms, data organization must be amenable to data-parallel processing

- May require programmer creativity, alternative algorithms

- Data-reorganization penalties can be significant

Compilers generally don't use SIMD capabilities

Most effective on algorithms that process large blocks of data

© 2005 Berkeley Design Technology, Inc.

### Microprocessors vs. DSPs: Fundamentals and Distinctions

## **Comparing DSPs and GPPs** Addressing Low-end and High-Low-end and High-Performance DSP Performance GPP Dedicated address-Often, no separate addressgeneration units generation units Specialized addressing General-purpose addressing modes modes Autoincrement Modulo (circular) · Bit-reversed (for FFT) © 2005 Berkeley Design Technology, Inc.

© 2005 Berkeley Design Technology, Inc.

Caches: Challenges

Caches work by lowering average access time

- They are effective at doing this in many applications

- But access times vary significantly

Some applications are sensitive to maximum access time (not average)

E.g., many "hard-real-time" signal processing applications

Signal processing access patterns often predictable

- Thus, DMA may be preferable to a cache

- Some recent caches provide pre-fetching capability

- Some DSP's caches can be locked or configured as part cache, part SRAM

© 2005 Berkeley Design Technology, Inc.

28

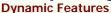

**Dynamic Features**

Dynamic features are used heavily in high-end GPPs to boost performance

- Superscalar execution

- Caches

- Branch prediction

- Data-dependent instruction execution times

These features are occasionally used in DSPs, too

These features complicate software development for real-time DSP applications

- Ensuring real-time behavior

- Optimizing code

© 2005 Berkeley Design Technology, Inc.

29

## **Comparing DSPs and GPPs**

#### **Low-end GPPs and DSPs**

#### GPPs:

Dynamic caches common

#### DSPs:

- Rarely have dynamic features

- Small "loop buffer" instruction cache exception

## High-Performance GPPs and DSPs

GPPs: Moderate to extensive use of dynamic features

- Dynamic caches standard

- Superscalar execution, branch prediction common

DSPs: Generally avoid dynamic features

- Dynamic cache is most common dynamic feature

- · Superscalar execution rare

- Branch prediction sometimes used

© 2005 Berkeley Design Technology, Inc.

0

## **Parallelism**

### Key implications of differences

- Cycle efficiency

- DSPs have advantage on signal processing tasks

- But may require special software development strategies—like assembly level programming—to realize full advantage

- Memory use efficiency

- Multi-operation instructions give DSPs advantage on signal processing tasks

- But GPPs often better on non-signal processing tasks—which typically consumes most of the code space

- Compiler friendliness

- · GPPs generally have the advantage

- · SIMD difficult for compilers, whether GPP or DSP

- Often requires assembly programming or use of high level intrinsics—both of which complicate software development

© 2005 Berkeley Design Technology, Inc.

31

**On-Chip Integration**

Low-end GPPs and DSPs

Typically, wide range of on-chip peripherals and I/O interfaces

Often oriented towards consumer applications

E.g., video coprocessors, USB ports, ... <u>High-Performance GPPs</u> and DSPs

Moderate to extensive onchip integration

PC CPUs offer very little on-chip integration

Often oriented towards communications infrastructure

E.g., Viterbi decoding coprocessors, UTOPIA ports, ...

© 2005 Berkeley Design Technology, Inc.

33

## **Comparing DSPs and GPPs**

**Compatibility and Availability**

**Low-end DSP**

Mostly proprietary architectures

I.e., one architecture, one vendor

Limited (at best) compatibility between successive generations

Occasionally available as licensable core

© 2005 Berkeley Design Technology, Inc.

#### **Low-end GPP**

Many shared architectures

I.e., one architecture, several (to many) vendors

Often binary compatibility between successive generations

Often available as licensable core

• E.g., ARM, MIPS

34

**Compatibility and Availability**

#### **High-Performance DSP**

**High-Performance GPP**

Mostly proprietary architectures

Exceptions: StarCore, ZSP

Mostly shared architectures

PowerPC, MIPS, ARM, x86

Sometimes binary compatibility between successive generations

• E.g., 'C6xxx, StarCore, ZSP

Usually binary compatibility between successive generations

Sometimes available as licensable core

E.g., StarCore, CEVA-X, ZSP

Sometimes available as licensable core

• E.g., ARM, MIPS

© 2005 Berkeley Design Technology, Inc.

35

## **Comparing DSPs and GPPs**

#### **Development Support**

|                                | DSPs                                              | GPPs                                            |

|--------------------------------|---------------------------------------------------|-------------------------------------------------|

| Tools                          | Primitive to moderately sophisticated             | Primitive to very sophisticated                 |

| DSP-specific tool              | Good to excellent                                 | Poor but improving                              |

| support                        | E.g., cycle-accurate simulators, DSP C extensions | E.g., general lack of cycle-accurate simulators |

| 3rd-party DSP software support | Poor to excellent                                 | Limited but growing                             |

| Non-DSP 3rd-party              | Poor                                              | Extensive                                       |

| software support               | Few to moderate RTOS options                      | Few to extensive RTOS options                   |

| Links w/other high-level tools | E.g., MATLAB                                      | E.g., GUI builders                              |

© 2005 Berkeley Design Technology, Inc.

36

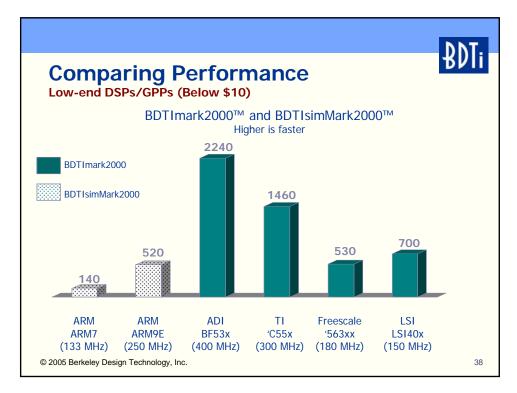

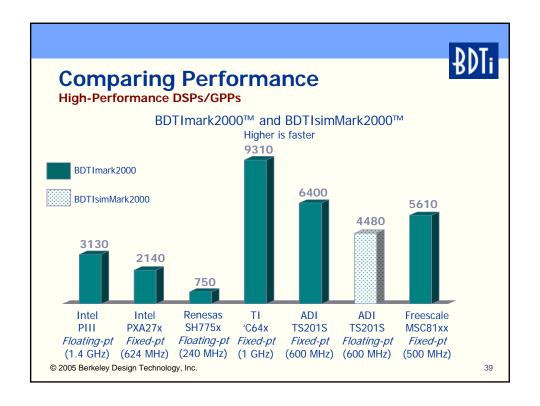

## **Comparing Performance**

When evaluating processors for signal processing, application-specific, product-specific considerations dominate

Relative performance can vary dramatically depending on the benchmark

Vendor performance claims should be viewed skeptically

- "MIPS" = ...

- Benchmarks are a sharp tool

#### Performance is more than speed

· Cost/perf, energy efficiency, memory use...

© 2005 Berkeley Design Technology, Inc.

37

© 2005 Berkeley Design Technology, Inc.

#### Microprocessors vs. DSPs: Fundamentals and Distinctions

#### When to Use Which **DSP GPP** Heavy signal processing Modest signal processing requirements requirements Limited control processing Extensive control processing Especially if code density and portability are important The DSP is incumbent The GPP is incumbent Software compatibility Software compatibility between generations not required—or can be achieved w/ DSP between generations required Multi-vendor architecture Multi-vendor architecture not desired desired GPP has better integration for application DSP has better integration for application © 2005 Berkeley Design Technology, Inc.

### When to Use Which

**Challenges in Using GPPs for Signal Processing Tasks**

Not enough DSP horsepower

Usually an issue only for very low-end GPPs or very demanding applications

Limited memory bandwidth

Again, mostly an issue for low-end GPPs

Lack of execution-time predictability

High cost, power consumption

True of PC CPU class GPPs

Few DSP-oriented development tools

E.g., lack of cycle-accurate simulators

Few DSP-oriented software libraries

Limited on-chip integration in some cases

© 2005 Berkeley Design Technology, Inc.

41

## When to Use Which

Limited data-type agility

Focus on 16-bit fixed-point

Momentum of popular GPP architectures

Generally inferior tools (except for DSP-oriented features)

Inferior third-party support for non-DSP tasks

• E.g., RTOSs

Proprietary architectures

© 2005 Berkeley Design Technology, Inc.

42

### **Conclusions**

**Take-Away Points**

When either a GPP or DSP is fast enough, other factors become prominent:

- Energy efficiency

- Integration

- · Compatibility, availability

- Multi-vendor architectures

- Licensable cores

- Tools

- DSP-oriented

- General-purpose

- Software

© 2005 Berkeley Design Technology, Inc.

43

## **Conclusions**

Will DSP-Capable GPPs Render DSPs Obsolete?

No, but they will pose increasingly strong competition

• Why have GPP+DSP if GPP alone is good enough?

Demands of most communications and mediaprocessing applications will continue to favor DSPs

Software infrastructure is key

- DSPs have the advantage for DSP tasks

- GPPs have the advantage for other tasks

For DSPs, the competitive field has become much larger

Differentiating criteria are changing

© 2005 Berkeley Design Technology, Inc.

44

### Microprocessors vs. DSPs: Fundamentals and Distinctions

# For More Information... www.BDTI.com

Inside [DSP] newsletter and quarterly reports Benchmark scores for dozens of processors Pocket Guide to Processors for DSP

Basic stats on over 40 processors

Articles, white papers, and presentation slides

- Processor architectures and performance

- Signal processing applications

- Signal processing software optimization comp.dsp FAQ

2004 Edition