## Conclusions

**Comparing Processors**

- Performance is interesting, but other factors are equally important

- Architecture is interesting, but it isn't all-important

- Compare processors the way you'd compare cars

- Not exclusively on their top speed

- Suitability for the task at hand

- "Cost of ownership"

- Time to market, ease of use, ...

© 2001 BDTI

| TMS<br>Impro          |                        |          | • |               |         |         |           |     |

|-----------------------|------------------------|----------|---|---------------|---------|---------|-----------|-----|

| ʻC62x                 | Exec Packet 1          |          |   | Exec Packet 2 |         |         |           |     |

| Fetch<br>Packet 1     | ins1                   | 2        | 3 | ins1          | 2       | NOP     | NOP       | NOP |

|                       | Exec Packet 3          |          |   |               | Exec P  | acket 4 |           |     |

| Fetch<br>Packet 2     | ins1                   | 2        | 3 | 4             | ins1    | 2       | NOP       | NOP |

| <i>'C64x</i><br>Fetch | <b>x</b> Ex            | ec Packe |   |               | acket 2 |         | kec Packe |     |

| Packet 1              | ins1                   | 2        | 3 | ins1          | 2       | ins1    | 2         | 3   |

| Fetch                 | Packet 3 Exec Packet 4 |          |   | Exec Packet 5 |         |         |           |     |

|                       | 4                      | ins1     | 2 | ins1          | 2       | 3       | 4         | 5   |

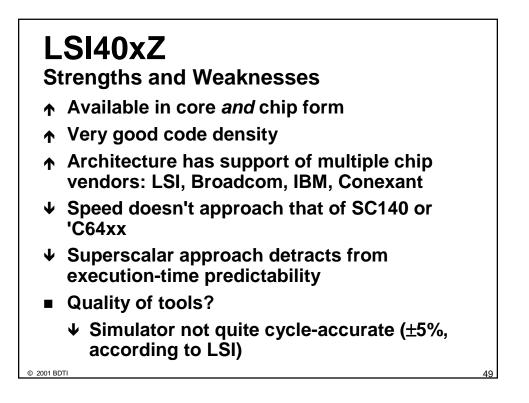

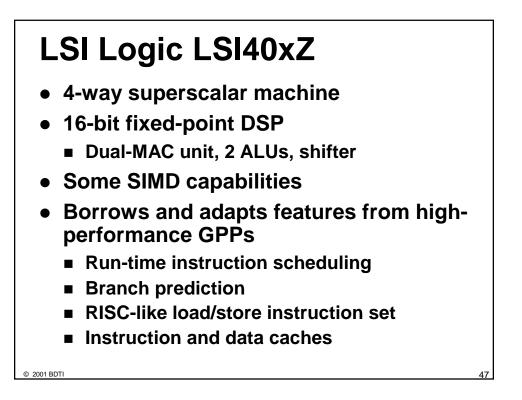

## LSI40xZ

- LSI Logic is using the core for:

- ASICs

- ASSPs

- General-purpose DSPs

- Licensing

- IBM, Broadcom, Conexant have licensed

- Emphasizing communications infrastructure applications

- At 200 MHz, a moderately highperformance DSP

- Leading speed in 1998; less so today

© 2001 BDTI