Updated October 2009 Copyright © 2009 Berkeley Design Technology, Inc. No reproduction or reuse is permitted without the express authorization of BDTI.

All processors benchmarked with 16-bit fixed-point data. All cores include at least 16 KB on-core memory and use worst-case clock speeds for theTSMC CLN65GP process and the Artisan Advantage core cell library. Vendors can choose different speed/area/power trade-offs; to understand the trade-offs, please view all BDTI metrics for each core. BDTIsimMark2000<sup>™</sup> scores may be based on projected clock speeds. For information, see www.BDTI.com/Services/Benchmarks.

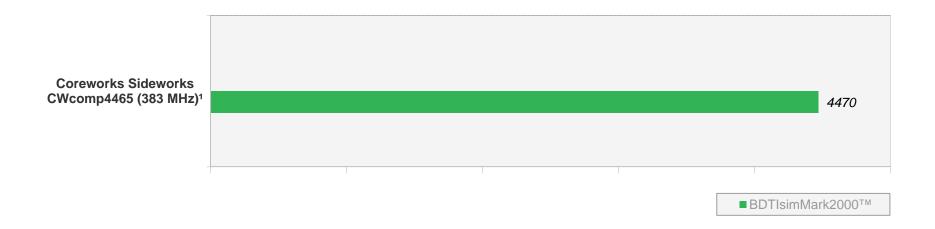

<sup>1</sup>Coreworks scores include both a customized SideWorks DSP engine and the FireWorks 32-bit RISC processor. The SideWorks core used to implement the BDTI DSP Kernel Benchmarks includes four 16-bit multiplier units, six 32-bit ALUs, five shift units, six data multiplexing units, two data de-multiplexing units, two bit-reverse units, a bit unpack unit, and 6K bytes of memory. Different versions of the SideWorks core will yield different performance, power consumption, and die size figures than those reported here.