© 1999 Berkeley Design Technology, Inc.

| FIR                                                                               | Filtering on the 'C62xx                                                                                                                                                                     |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Can execute<br>up to eight<br>32-bit<br>instruction <del>s →</del><br>in parallel | LOOP:<br>ADD .L1 A0,A3,A0<br>  ADD .L2 B1,B7,B1<br>  MPYHL .M1X A2,B2,A3<br>  MPYLH .M2X A2,B2,B7<br>  LDW .D2 *B4++,B2<br>  LDW .D1 *A7,A2<br>  [B0] ADD .S2 -1,B0,B0<br>  [B0] B .S1 LOOP |

| dotprod:                                                                          | <pre>onventional DSP (ss), MX0=DM(I0,M0),MY0=PM(I4,M4); © 1999 Berkeley Design Technology, Inc.</pre>                                                                                       |

© 1999 Berkeley Design Technology, Inc.

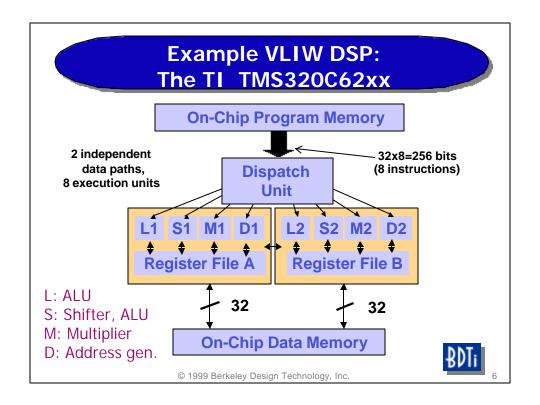

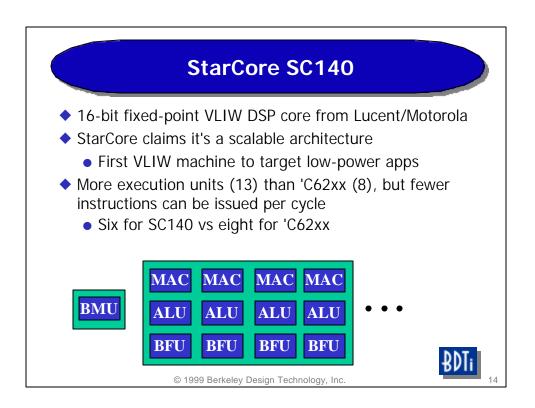

| Processor   | Issue<br>width | Data memory<br>bandwidth<br>(16-bit words) | Instruction size              | Clock<br>(MHz) | Pipeline<br>depth | Notable<br>characteristics         |  |  |

|-------------|----------------|--------------------------------------------|-------------------------------|----------------|-------------------|------------------------------------|--|--|

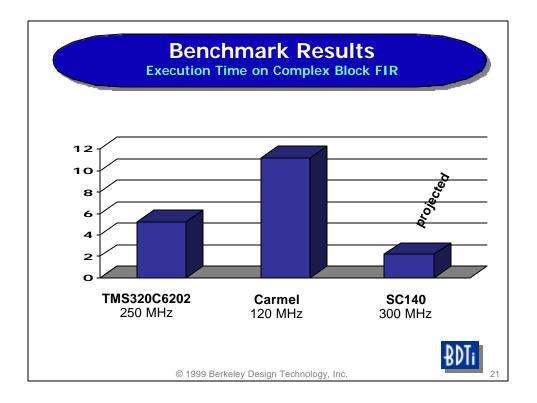

| TMS320C62xx | 8              | 4 words/cycle                              | 32 bits                       | 250            | 11                | 1st VLIW-based<br>DSP processor    |  |  |

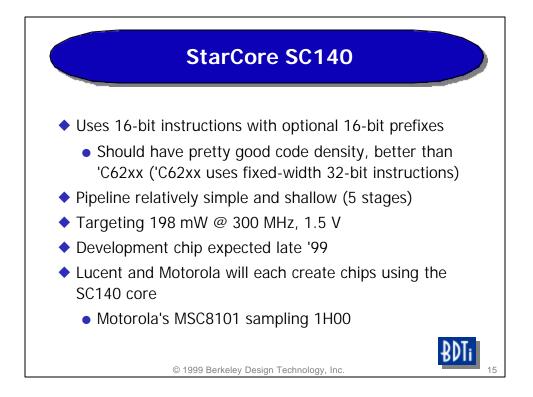

| SC140       | 6              | 8 words/cycle                              | 16 bits w/<br>16-bit prefixes | 300*           | 5                 | Scalable, approach to compact code |  |  |

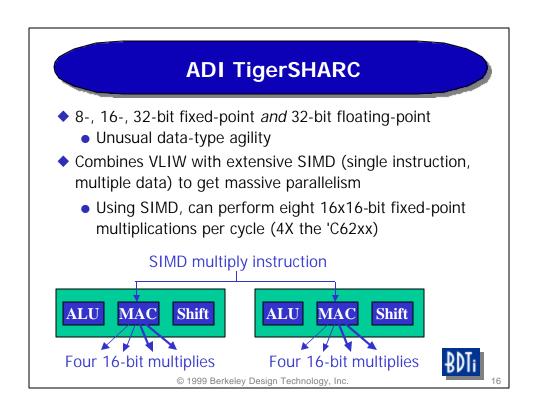

| TigerSHARC  | 4              | 16 words/cycle                             | 32 bits                       | 250*           | 8                 | SIMD + VLIW,<br>data type agility  |  |  |

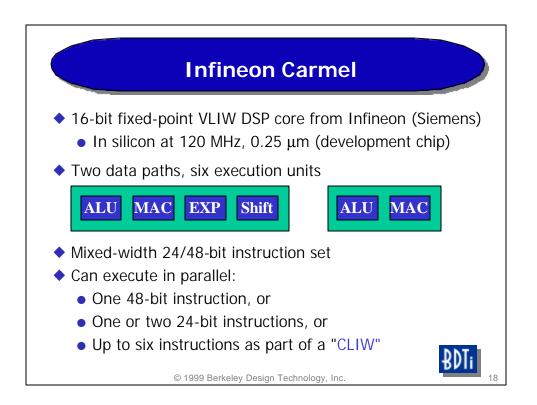

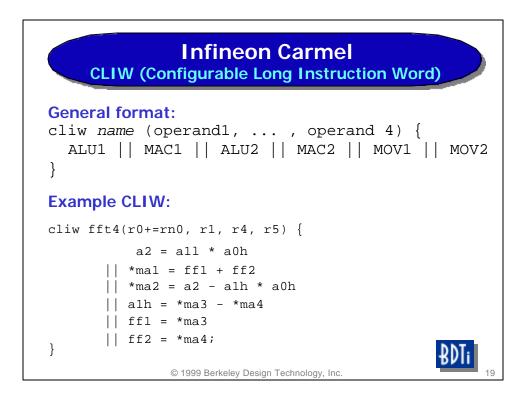

| Carmel      | 2,6            | 4 words/cycle                              | 24/48 bits                    | 120            | 8                 | CLIW instructions<br>4 AGUs        |  |  |

| -           |                |                                            |                               |                |                   | CLIW instruct                      |  |  |

© 1999 Berkeley Design Technology, Inc.

© 1999 Berkeley Design Technology, Inc.